## Improvements in P/AI High Efficiency Technology, AISi

(Mejoras en tecnología fósforo-aluminio de alta eficiencia)

Doctoral thesis

By Muhammad Azam Rasool

Thesis directors:

Dr. José Rubén Gutiérrez

Dr. Juan Carlos Jimeno

July 2016

#### **DEDICATED**

#### TO

### My Parents (late) WHO SET A MODEL ROLE FOR MY LIFE

#### **ACKNOWLEDGEMENTS**

All praises for **Almighty ALLAH**, Who is most Omnificent, Omniscient, Omnipotent and Omnipresent for giving me the will and strength to accomplish this job. I am showing my humble submission to the heart and soul of the world and the world here after The **Holy Prophet Muhammad** (Peace be upon him), whose life is an ideal pattern for me.

I owe a deep depth of gratitude to my ingenious, awesome, martinet and a nonpareil thesis directors **Prof. Dr. Juan Carlos Jimeno** and **Dr. José Rubén Gutiérrez** for their keen interest, valuable suggestions, constant encouragement and precious attentions throughout the course of this investigation. The whole work is carried out and completed at Technological Institute of Microelectronics (TiM), Technological park of Zamudio, TiM lab, building 105, University of the Basque Country, EHU/UPV, Basque country Spain under the supervisions of **Prof. Dr. Juan Carlos Jimeno** and **Dr. José Rubén Gutiérrez.** Their precious attention, continued interest, guidance and inspiration throughout my research work support me for the completion of this thesis.

In addition to this I am very thankful to the director of institute of Microelectronics, **Prof. Dr. Juan Carlos Jimeno** and jury members of TiM for providing me a research grant to complete this work at TiM.

I owe my deepest gratitude to **Dr. Rosa Lago (Ex TiM faculty member)** for her supervision on research work "improvement in P/Al high efficiency technology" during first year of my stay at TiM, I am also very thankful to all faculty members of TiM, Dr. Fede, Dr. Victor, Dr. Velia, Dr. Carmen, Fernando and Maria Jose for their guidance, nice hospitality and help during my stay at TiM and in Bilbao.

I sincerely thanks to my senior colleagues, **Dr. Vanesa Fano (especially), Aloña Otaegi, Dr. Eneko and Dr. Nekane** for their guidance to precious suggestions and collaborating during the course of this thesis. They help in that time when they were busy in their own thesis work.

I should like to express my sincere gratitude to my ex-colleagues. Former lab members of TiM, **Ahmad Habib**, **Itraxe**, **Cristina** and **Jorge** for their cooperation, help and guidance. I am thankful to **Urko Gutiérrez**, technical staff member of TiM, who helped me not only in lab work but also help me to solve the difficulties which I was facing outside from TiM.

At the end, I am thankful to **my sister and my brothers**, for their prayers, unconditional love and encouragement.

Muhammad Azam Rasool (Bilbao Spain)

### Resumen

La tecnología de alta eficiencia P/Al fue desarrollada a mediados de los años 80 mediante estudios teóricos y experimentales de A. Cuevas y M. Balbuena en el IES-UPM. Ellos concluyeron que es posible obtener alta eficiencia con emisores de fosforo profundos poco dopados y contacto de aluminio en la superficie posterior (aluminum back surface field). El objetivo principal de este trabajo fue mejorar la tecnología P/Al de alta eficiencia en el caso de obleas finas de silicio de bajo grado para células solares industriales.

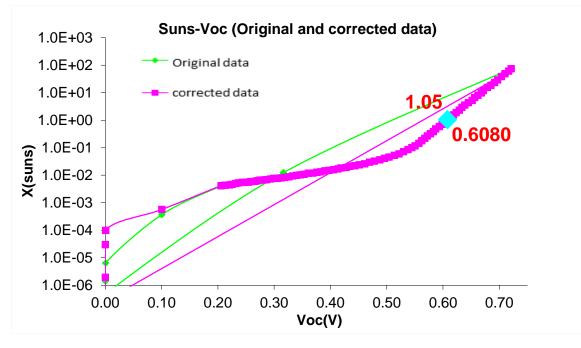

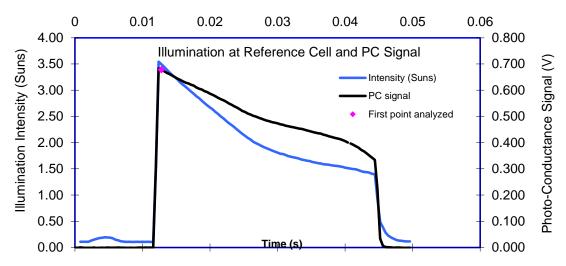

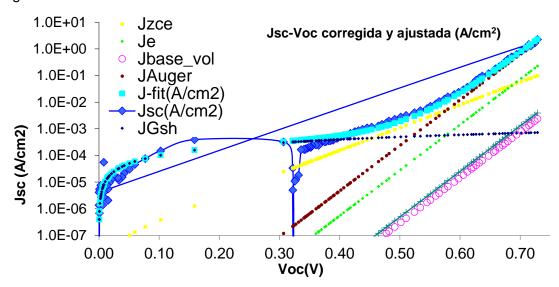

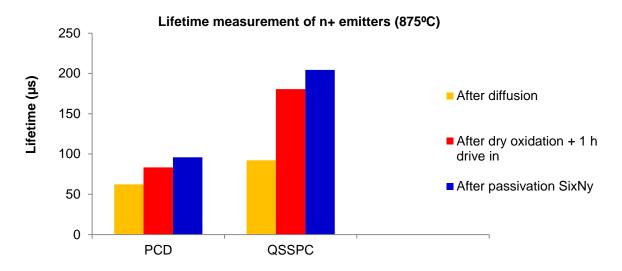

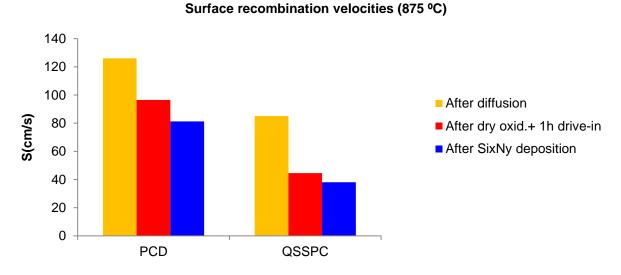

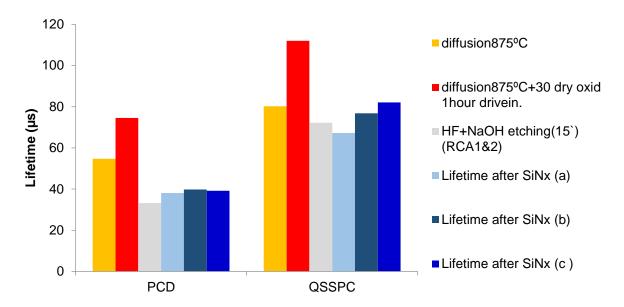

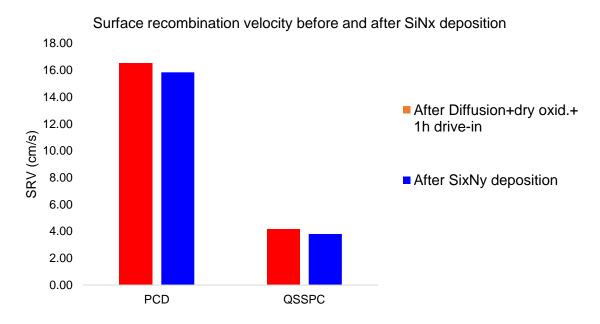

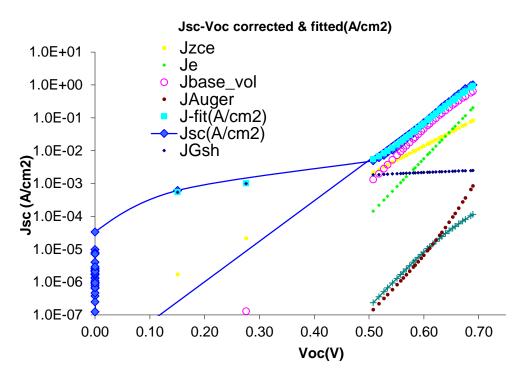

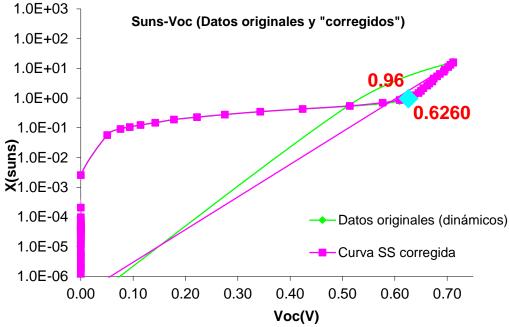

Aplicando la tecnología P/AI, se han realizado diferentes lotes de células solares y su caracterización se llevó a cabo mediante medidas de Soles-Voc, tiempo de vida y curvas IV. Hemos observado alta densidad de corriente de saturación del emisor en la fabricación de emisores, que limita el voltaje de circuito abierto, estando en el rango de 1E-11A/cm² para los peores emisores y 5E-13 A/cm² para los emisores buenos. La máxima eficiencia que hemos obtenido se situaba en torno a 16.5%. El voltaje de circuito abierto de las células estaban en el rango de 600mV a 610mV y la corriente de cortocircuito estaba en el rango de 36mA/cm² a 39.2mA/cm². Hemos medido el tiempo de vida de las células P/AI después de cada paso térmico y después de la deposición de SiNx por PECVD, el máximo tiempo de vida que estaba en torno a 20µs por la técnica PCD y 40 µs por la técnica QSSPC después de la deposición de SiNx.

Debido a la poca eficiencia y la pobre calidad de la pasivación del emisor, hemos planeado investigar la difusión de fosforo en profundidad con el objetivo de lograr emisores profundos, ligeramente dopados y pasivados. Hemos llevado a cabo varias experimentos en de difusiones de fosforo a cuatro temperaturas en el rango de 800 a 875 °C con el fin de lograr emisores n+ profundos y ligeramente dopados y sus perfiles. La densidad de corriente de saturación que limita el voltaje de circuito abierto depende de la concentración de fosforo activo y la profundidad de la unión. Debido a la alta temperatura, la difusión de fosforo forma una capa muerta que aumenta la recombinación y disminuye la eficiencia de la célula. Se introduce un paso de oxidación húmeda y/o seca para minimizar el efecto de la capa muerta. El porcentaje de fosforo eléctricamente activo se calcula por el modelo Tsai. Nuestros resultados muestran que con el aumento de temperatura, la concentración de Fosforo eléctricamente activo disminuye y viceversa. El objetivo de este estudio era realizar un proceso de difusión en un solo paso en el horno para la fabricación industrial de células solares.

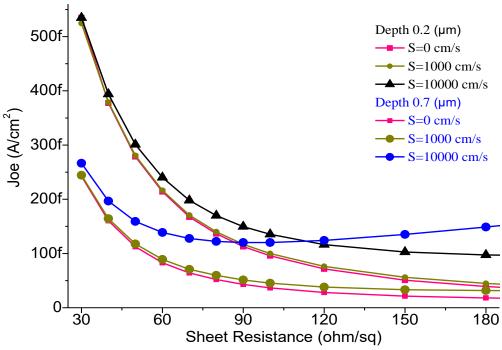

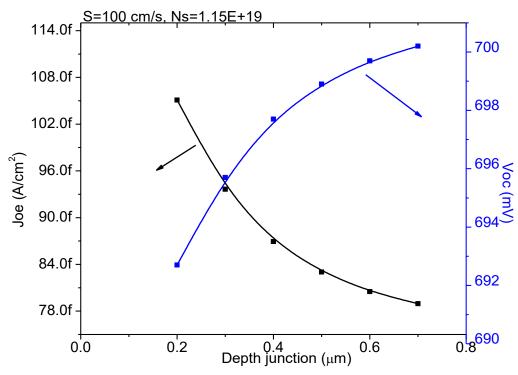

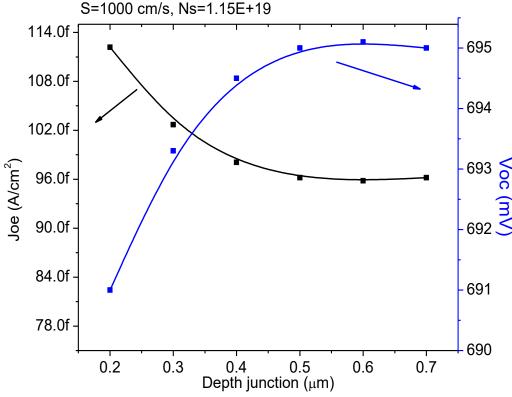

La fiabilidad de los emisores fue evaluada por la influencia de la pasivacion. Para las condiciones de superficie de cada emisor, las velocidades de recombinación superficiales han sido simuladas en el PC1D para emisores convencionales con una profundidad de unión de unión de 0.2 µm y para los emisores actuales con una profundidad de union de 0.7 µm, mostrandose que los emisores con una union profunda dan bajos valores de densidad de corriente de saturacion de emisor (Joe) en compraracion con una profundidad de union convencional. Los emisores obtenidos en un unico paso termico estan en torno a 7-8 x10<sup>19</sup> cm<sup>-3</sup> con una resistencia de capa de ~60  $\Omega$ / $\square$  y una profundidad de union de 0.71 µm y una densidad de corriente de saturacion de emisor de 130 fA/cm<sup>2</sup>. En el proceso de difusión de una sola etapa, el gettering es mucho mayor que el obtenido con el proceso convencional y la carga térmica es también baja. En el caso de sustratos de tipo-p

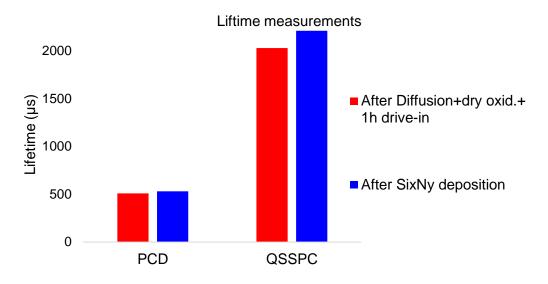

y alta resistividad de  $5.4\Omega$ .cm, hemos medido tiempos de vida de en torno a 200 µs y en las obleas de tipo —n de baja resistividad (0.8  $\Omega$ .cm) en torno a 505 µs por la técnica PCD. La mejora en tiempo de vida es mucho mayor que en los procesos de gettering convencionales.

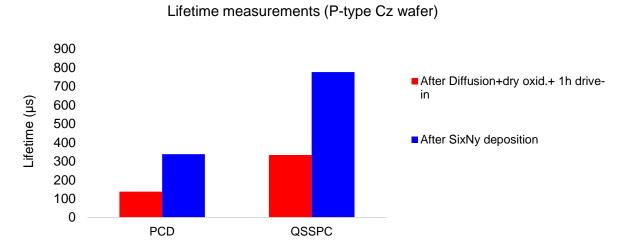

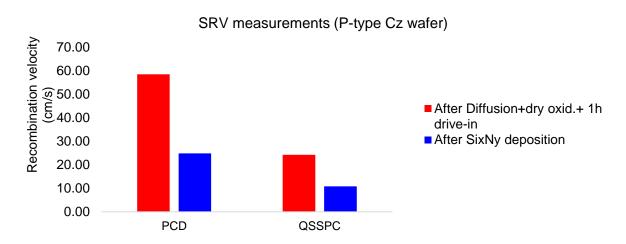

Utizandose una receta de SiNx optimizada, el tiempo de vida máximo que se midio en una estructura SiO2/SiNx para un emisor pasivado fue 334 µs por la tecnica PCD y 780 µs por la técnica QSSPC que se corresponde con una velocidad de recombinación superficial (SRV) de 10 cm/s para la técnica QSSPC y 24 cm/s por la técnica PCD para obleas de tipo p y en obleas de tipo n, el tiempo de vida máximo fue 1263 µs por la técnica PCD y 2209 µs por la técnica QSSPC que se corresponde con una veloscidad de recombinación superficial efectiva de 3.8 cm/s pr la técnica QSSPC y 15cm/s por la técnica PCD. La densidad de corriente de saturación del emisor (Joe) disminuye aun más debido al efecto de SiNX que pasa a estar en el rango de 5E-14 a 2.5E-14A/cm² (25-25fA/cm²) para obleas de tipo p.

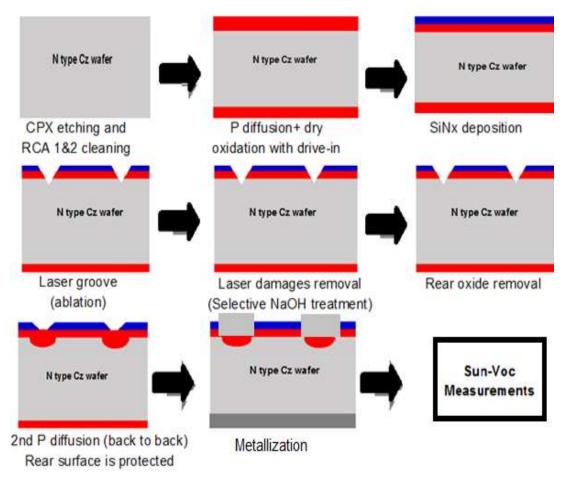

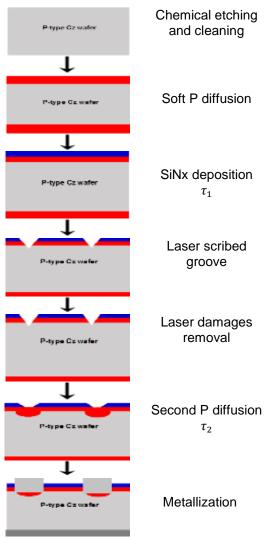

Para emisores suavemente dopados (resistencia de capa  $100\text{-}200\,\Omega/\Box$ ), es difícil hacer contacto entre el metal frontal y los emisores suavemenete dopados. Este tema puede superarsepor la fabricación de emisores selectivos. Los emisores selectivos tienen alta concentración de dopado bajo la red de contactos metalicos y baja concentración de dopaje en la zona iluminada. La segunda difusión de fosoforo (parte posterior- parte posterior) se realizó a 875 °C durante 30 minutos en la area de surcos creadas con el láser, protegiendo la superficie posterior y el resto del area frontal con una capa SiNx para crear emisores selectivos. Una capa gruesa de Aluminio se depositó en la parte posterior de las células por medio de serigrafía con el fin de crear back surface field (BSF) asi como contacto posterior. La temperatura óptima para el contacto de Aluminio es 925 °C a 60 pulgadas/min de veloicidad de cadena para tener un buen quemado y contacto. En este paso, la superficie posterior Al-BSF con oxido de Silicio (SiO2) muestra alto voltaje de circuito abierto y bajo valor de Joe.

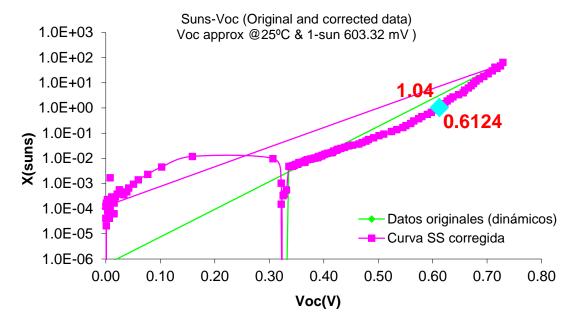

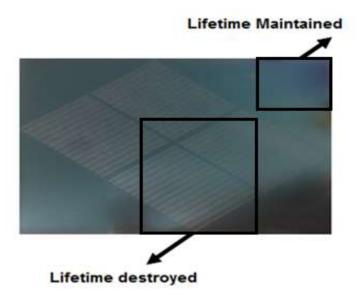

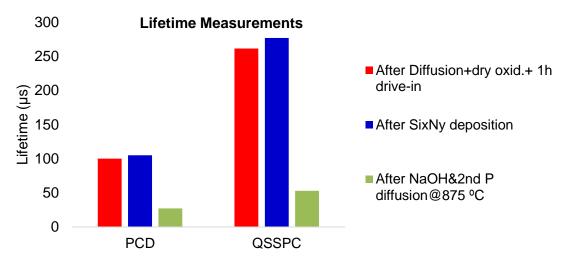

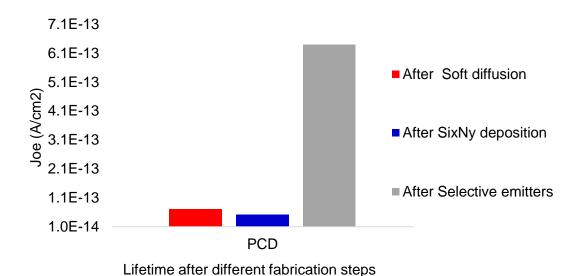

Tras la formación de contactos posteriores, hemos medido los Soles-V<sub>OC</sub> de las células para obtener los parámetros eléctricos de las células solares, hemos encontrado que la densidad de corriente de saturación (Joe) de las células aumentó, las cuales estaban en el rango de 6.45E-13 a 3.1E-12A/cm² y shunt conductance estaban en el rango de 2E-4 a 3.5E-3 ohm.cm². Esta Joe es debida a los emisores posteriores (Al-BSF), debemos optimizar algunos parámetros para una apropiada metalización, tales como la pasta de metalización con el fin de medir los valores reales (bajo) de la Joe de las células. La calidad de los emisores selectivos está afectada por el tratamiento químico, este fenómeno se observo tras las medidas de tiempo de vida de los emisores selectivos, hemos encontrado reducción en el tiempo de vida, lo que habíamos medido tras la deposición de la capa SiN<sub>x</sub> pero el tiempo de vida se mantiene homogénea en la zona de dopaje suave. La destrucción del tiempo de vida se reduce cuando se ha utilizado baño de teflón para el tratamiento químico en vez del baño metálico. El NaOH o el KOH se utiliza para eliminar los daños del láser previo a la segunda difusión de P. Utilizándose KOH, la reducción en tiempo de vida es menor que en el caso de la NaOH.

Hemos medido valores de Soles-V<sub>oc</sub> en torno a 624 mV para obleas de tipo-p de alta resistividad y 626mV para las obleas de tipo n de baja resistividad. El comportamiento final de la célula P/AI es debido al AI-BSF, puede ser mejorada más y teóricamente se espera que sea en torno a 650 mV. El proceso que se ha utilizado para fabricar los emisores selectivos es factible para aplicarse en la fabricación industrial de células solares P/AI con emisores selectivos en los que se espera una eficiencia en torno al 20 %.

### Laburpena

Efizientzia altuko P/Al teknologia 1980ko erdialdean garatu zen A. Cuevasek eta M. Balbuenak IES-UPMn aurrera eramandako ikerketa teorikoak eta esperimentalak zirela medio. Haiek ondorioztatu bezala, arinki dopatutako fosforozko igorle sakonak eta aluminiozko BSFak erabilita (P/Al teknologia) efizientzia altuak lor zitezkeen. Lan honen helburu nagusia honako hau da: P/Al teknologia hobetzea, maila baxuko siliziozko olata finak erabilita, industriako eskakizunetara begira.

P/Al teknologiaren bitartez gabrikatu dira eguzki-zelula sortak eta Suns-Voc kurbak, bizialdia eta IV kurbak neurtu izan zaizkie horiek karakterizatzeko. Neurketen arabera, asetasuneko korronte-dentsitate altuak ikusi dira igorleen fabrikazioan, zirkuitu irekiko tentsioa mugatzen dutenak. Asetasuneko korronte dentsitatearen tartea 3·10<sup>-11</sup> cm²-tik (txarrena) 5·10<sup>-13</sup> A/cm²-ra (hoberena) artekoa da. Lortutako efizientzia maximoak 16.5 % ingurukoak dira; eguzki-zelulen zirkuitu irekiko tentsioa 600-610 mV tartekoa eta zirkuitu laburreko korronte-dentsitatea 36-39.2 mA/cm²-koa. P/Al eguzki-zelulen bizialdia neurtu da urrats termiko guztien ostean bai eta PECVDz SiNx geruzak ezarri ostean; SiNx geruza ezarri ostean neurtutako bizialdi maximoa, 20 μs ingurukoa da PCD bidez neurtuta eta 40 μs-koa QSSPC bidez neurtuta.

Igorleen pasibaketaren kalitate txikia eta efizientzia baxua dela eta, fosforozko dopaketak sakon aztertu dira, arinki dopatutako eta sakon pasibatutako igorleak lortu nahian. Horretarako, hainbat saiakera egin dira, fosforo-dopaketak 800-875 °C tartean lau tenperatura aukeratuta: jomuga arinki baina dopatutako n+ igorleak lortzea izan da, eta bide batez, haien profila. Igorlearen asetasuneko korrontea, zirkuitu irekiko tentsioa mugatzen duena, fosforo-kontzentrazioaren eta junturaren sakoneraren menpekoa da. Tenperatura altuak direla eta, fosforo-dopaketak geruza ahitu bat sortzen du, birkonbinazioa handitzen eta zelularen efizientzia txikitzen duena. Oxidazio lehor/heze bat gaineratzen zaio geruza ahituaren efektua txikitzeko. Elektrikoki aktiboa den fosforo portzentajea Tsai ereduaren bitartez kalkulatzen da. Emaitzen arabera, tenperaturak igo ahala elektrikoki aktiboak diren Pen kopurua txikitzen da eta alderantziz. Ikerketa honek labean gauzatutako urrats bakarreko dopaketa egitea zuen helburu, industrian fabrikatzen diren eguzki.zelulei-begira.

Igorleen fidagarritasuna pasibaketaren eraginaren bitartez aztertu da: igorleen gainazaleko baldintzaren arabera gainazaleko birkonbinazio-abiadurak simulatu dira PC1D bitartez: igorleek 0.7 μm-ko sakonera izanez gero, igorleen asetasuneko korrontedentsitatea txikia da ( $J_{0e}$ ) 0.2 μm-ko sakonera duten ohiko igorleekin alderatuta. Urrats termiko bakarrean gauzatutako igorleen kontzentrazioa 7-8 x10<sup>19</sup> cm<sup>-3</sup> –ko tartean dago, geruza-erresistentzia ~60 Ω/ $\Box$ -koa, junturaren sakonera 0.71 μm-koa eta igorlearen asetasuneko korronte-dentsitatea 130 fA/cm2. Pauso bakarreko dopatze-prozesuan *gettering*a handiagoa da, ohiko prozesuarekin alderatuta, gainera, gastu termikoa txikia da. Materiala p-motakoa bada 200 μs-ko bizialdiak neurtu dira erresistibitate altuko olatetan (5.4 $\Omega$ .cm) eta n-motako erresistibitate baxuko olatetan (0.8  $\Omega$ .cm) 505 μs-koak inguru (PCD teknika). Bizialdian hobekuntza ohiko gettering prozesuetan baino handiagoa da.

SiNx ezarketarako errezeta berria erabilita, optimizatutakoa, pasibatutako igorleetarako SiO2/SiNx egituran neurtutako bizialdi maximoa 334 µs-koa da, PCD bitartez

neurtutakoa eta 780 μs QSSPC teknikaren bitartez, hau da, 10 cm/s-ko SRV efektiboa QSSPCren bitartez eta 24 cm/s-ko SRV efektiboa QSSPCren bitartez p-motako olaten kasurako; n-motako olaten kasurako aldiz, neurtutako bizialdi maximoa 1263 μs-koa (PCD) eta 2209 μs-koa (QSSPC), hau da, 3.8 cm/s-ko SRV efektiboa (QSSPC) eta 15 cm/s-koa (PCD). Igorlearen asetasuneko korronte-dentsitatea hare gehiago jaitsi da, SiNx-ren pasibaketaren eraginez, p-motako olaten kasurako eta 5·10<sup>-14</sup>-2.5·10<sup>-14</sup> tartekoa izatera iristen da.

Arinki dopatutako igorleen kasuan (geruza-erresistentzia  $100\text{-}200\,\Omega/sq$ ), ez da erraza aurrealdeko metala eta igorlea kontaktatzea. Arazo horri nagusitu dakioke igorle selektiboak gauzatuz gero: aurrealdeko metalaren kontaktatze-eskualdeetan igorle selektiboak, kontzentrazio handikoak, ezarriko dira eta argiztapeneko eskualdeetan dopaketa baxuko igorleak gauzatuko dira. Igorle selektibo horiek gauzatzeko 2. dopaketa bat gauzatu da, olatak bizkarrez bizkar kokatuta (en *back to back*), 30 minutuz 875 °C-era laser bidez urratutako eskualdeetan; horretarako, olatak SiNx geruza batez babestuko dira lehenik eta behin, gero laser bidez urratu eta egitura horiek labean sartu. Aluminiozko geruza lodi bat ezarri zaie eguzki-zelulei atzealdean serigrafia bidez BSFa eta atzealdeko kontaktua gauzatzeko. Aluminiozko atzealdeko kontaktuen sinterizazioa zinta-labean egiteko tenperatura eta abiadura optimoak 925 °C eta 60 in/min dira; urrats horretan atzealdeko Al-BSF gainazala, siliziozko dioxidoa (SiO<sub>2</sub>) gainazalean duena, da zirkuitu irekiko tentsiorik altuena ematen duena, bai eta eta  $J_{0e}$ -eko baliorik baxuena ere.

Atzealdeko kontaktuak gauzatu ostean eguzki-zelulen karakterizazio elektrikoa egin da, Suns-V $_{OC}$  kurba ezaugarriak neurtuta. Gauzak horrela,  $6.45\cdot 10^{-13}-3.1\cdot 10^{-12}$  A/cm² tarteko  $J_{0e}$ -ak eta  $2\cdot 10^{-4}-3.5\cdot 10^{-3}$   $\Omega\cdot \text{cm}^2$ -ko shunt-konduktantziak neurtu dira.  $J_{0e}$ -a atzealdeko igorlearen ondoriozkoa da (Al-BSF): metalizazioa egokia izan dadin parametro batzuen optimizazioa beharrezkoa da, metalizazio-oreen optimizazioa, besteak beste,  $J_{0e}$ -ko balio errealak (baxuagoak) neurtzeko. Igorle selektiboen kalitatea tratamendu kimikoaren menpekoa da; igorle selektiboen bizialdia murriztu da (SiN $_{x}$  geruzaren ezarketaren ostean neurtutakoa); bestalde, bizialdia berdintsu mantendu da oro har igorle nagusiaren eskualdeetan. Bizialdiaren degradazioa, baina, txikiagoa izan da tefloizko bainua metalezkoaren ordez erabili denean. NaOH-zko edo KOH-zko soluzioak laser-kaltea txikiagotzeko erabili dira, bigarren fosforo-dopatzearen aurretik. Bizialdia gutxiago txikiagotzen da KOH-zko soluzioarekin NaOH-zko soluzioarekin baino.

Zirkuitu irekiko tentsioa 624 mV ingurukoak neurtu dira p-motako erresistibitate altuko olatetan, n-motako erresistibitate baxuko olatetan 626 mV ingurukoak. P/Al eguzkizelulen bukaerako bilakaera Al-BSFaren ondoriozkoa da: hobetu daiteke, teorikoki 650 mV-era arte. Igorle selektiboak gauzatzeko erabili den prozesua bideragarria da industria-fabrikazioan txertatzeko, eta horrela, 20 %-ko efizientzia duten igorle selektiboak dituzten P/Al eguzki-zelulak gauzatu daitezke.

### Summary

High efficiency P/AI technology was developed in the mid of 1980s by theoretical and experimental studies of A. Cuevas and M. Balbuena at IES-UPM. They have concluded that it is possible to obtain high efficiency with lightly doped deep phosphorus emitters and aluminum back surface field, P/AI (P emitters/AI BSF). The main objective of this work was to improve high efficiency P/AI technology by using low grade silicon thin wafers for solar cells for industrial application.

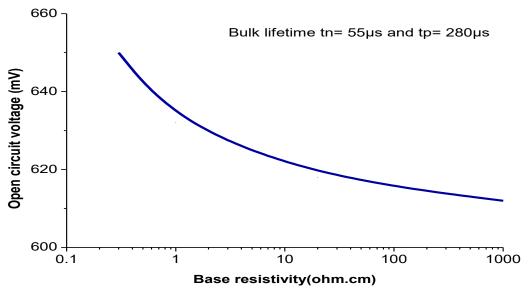

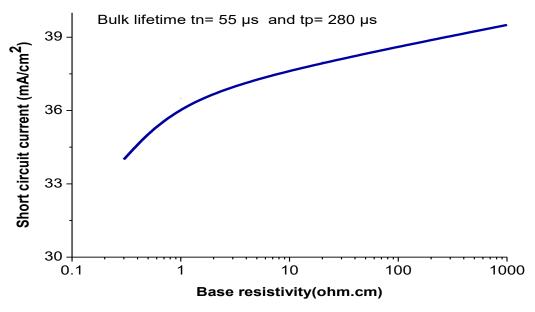

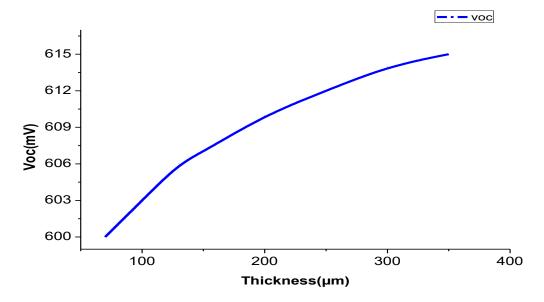

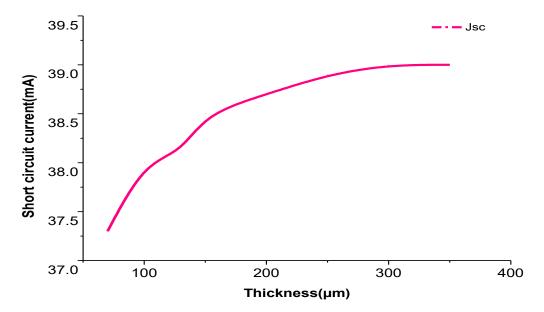

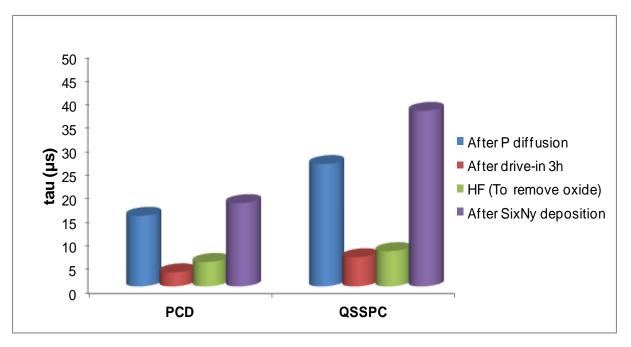

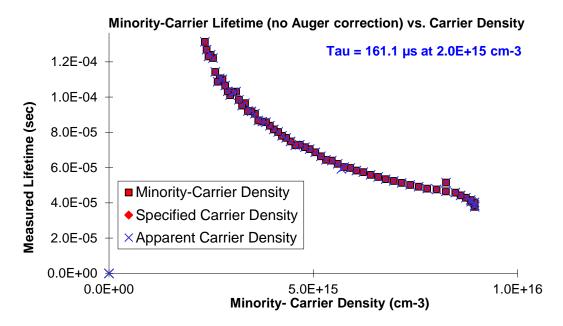

By applying P/Al technology, we have fabricated different batches of  $n^+p\ p^+$  (P/Al) solar cells and their characterization were carried out by Sun-Voc, lifetime and IV curves measurements. We have observed high emitter saturation current density in fabrication of emitters which limits the open circuit voltage were in range of 1E-11A/cm² for worse emitters and 5E-13 A/cm² for good emitters. Maximum efficiency which we have obtained was around 16.5%. Open circuit voltage of cells were in range of 600mV to 610mV and short circuit current was in range of 36mA/cm² to 39.2mA/cm². We have measured lifetime of P/Al solar cells after each thermal step and each after SiNx deposited by plasma enhanced chemical vapor deposition, the maximum lifetime which was around 20µs by PCD (transient photoconductance decay) and 40 µs By QSSPC technique (quasi steady state photo-conductance decay) after SiNx deposition.

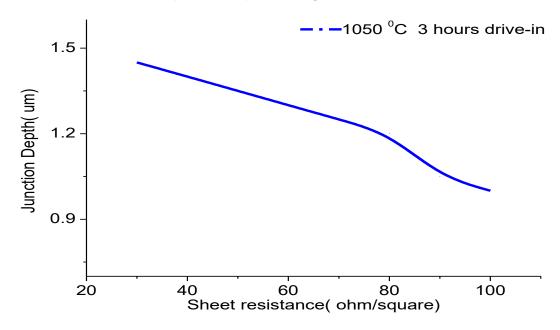

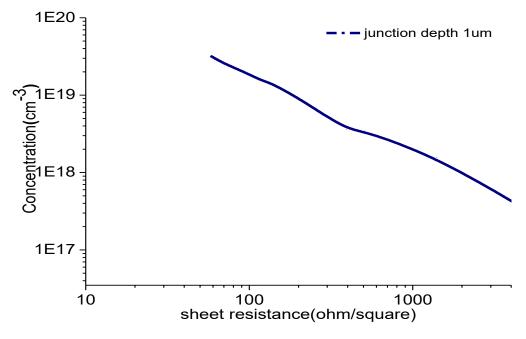

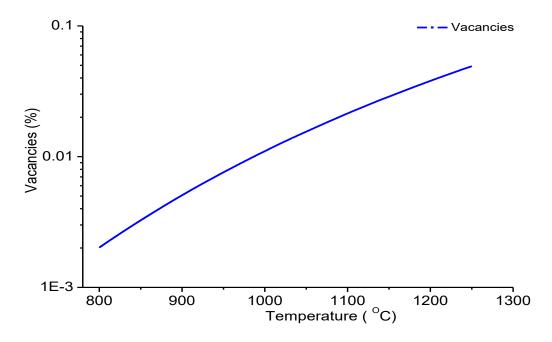

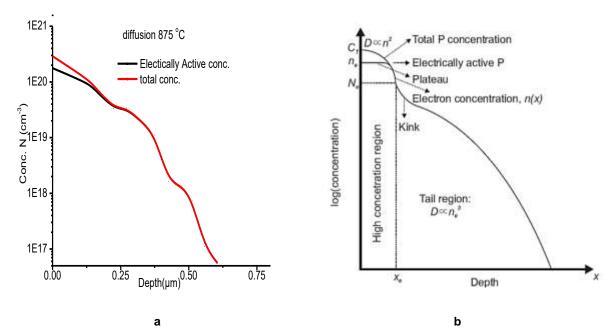

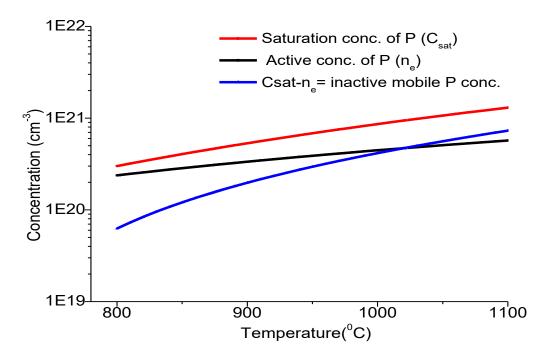

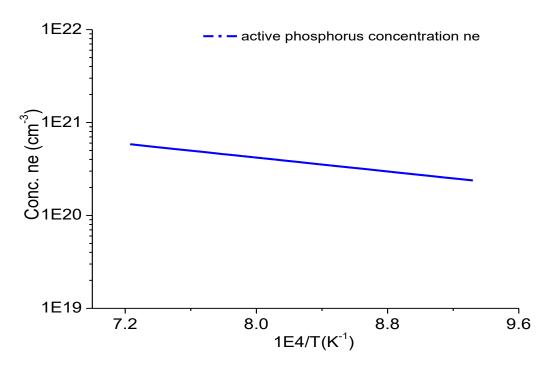

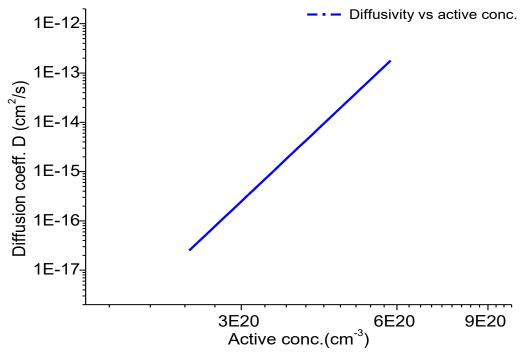

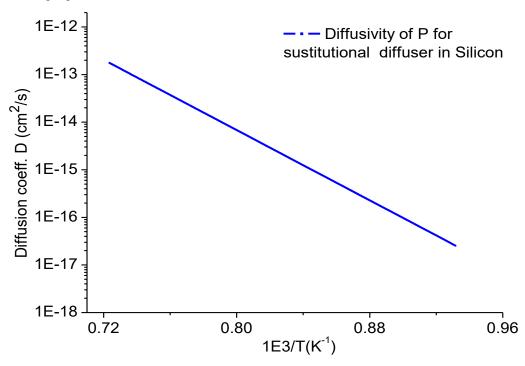

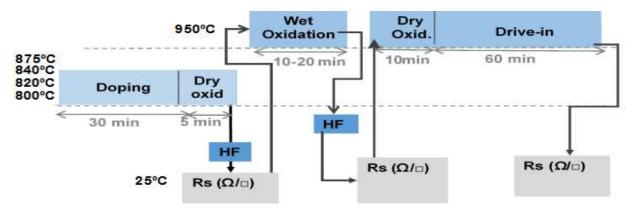

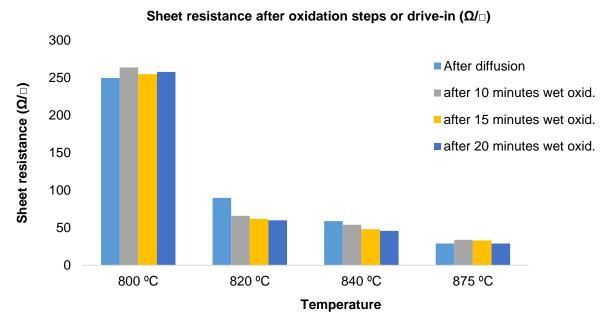

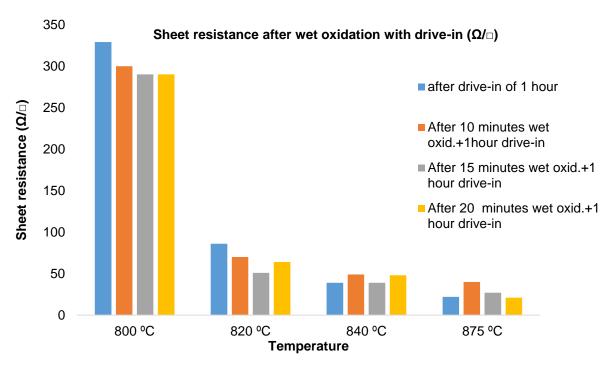

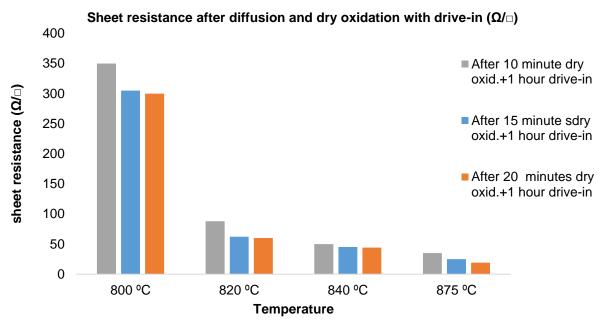

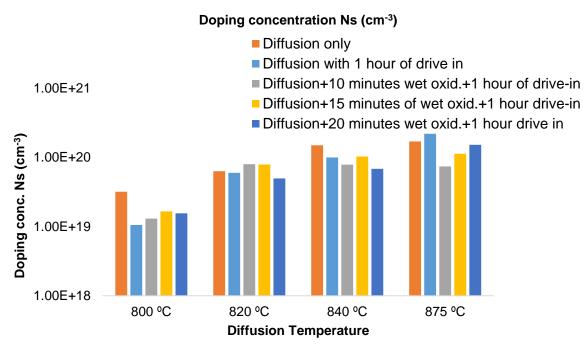

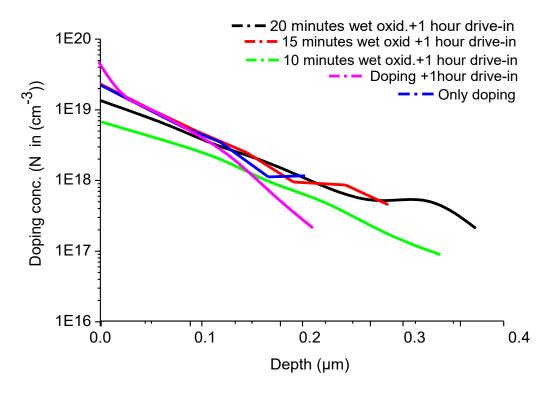

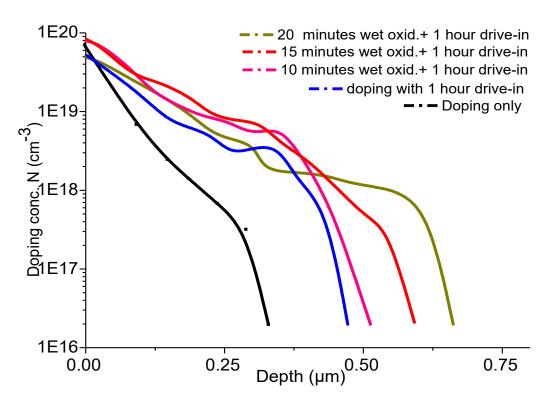

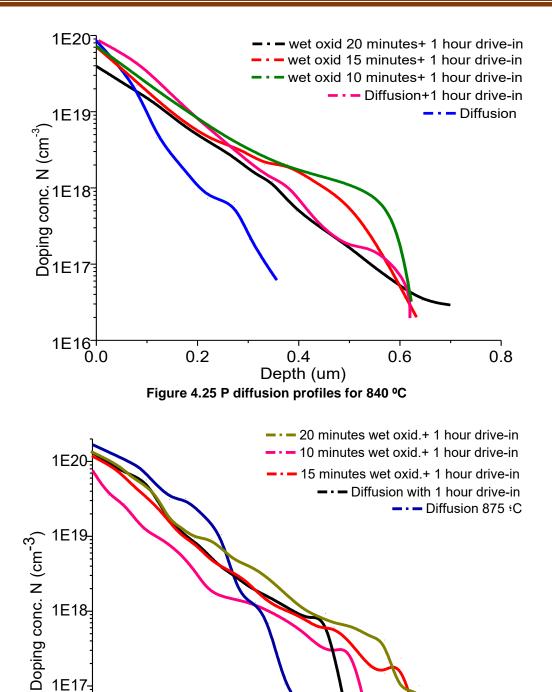

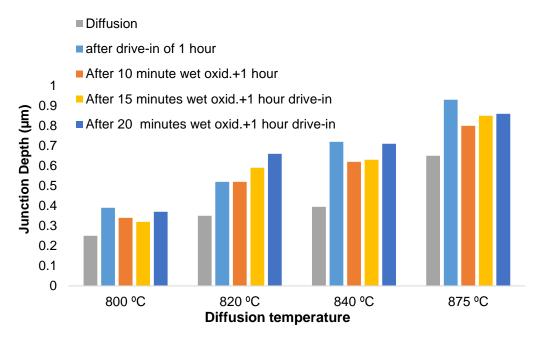

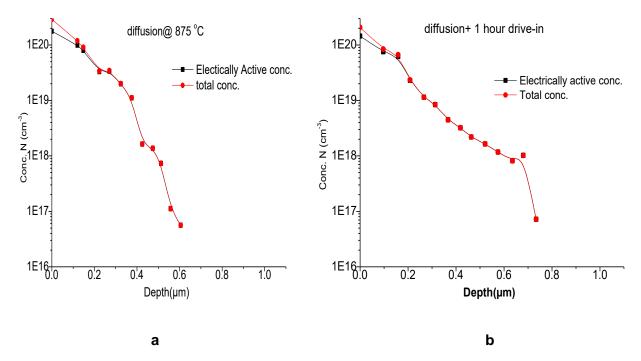

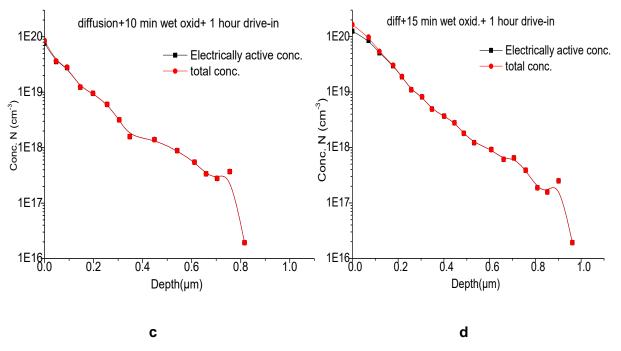

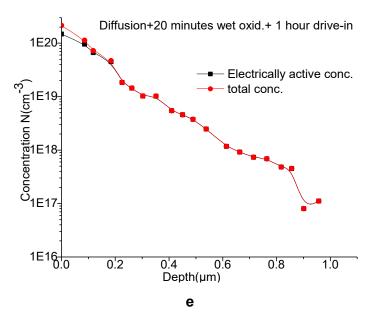

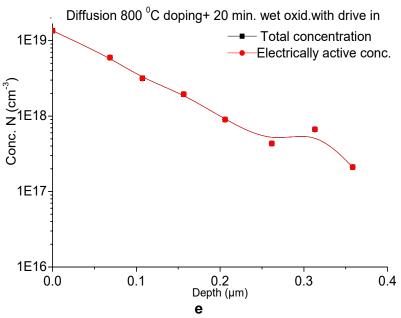

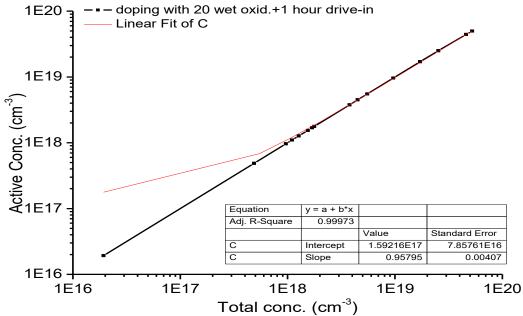

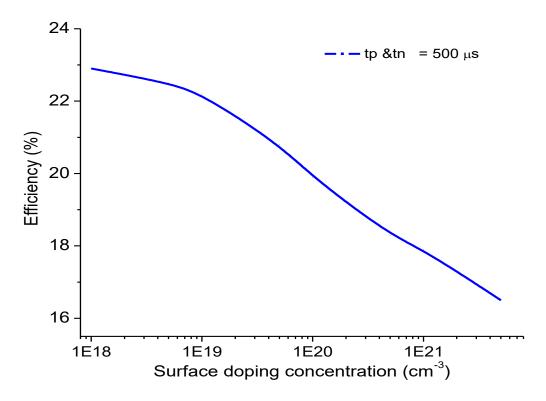

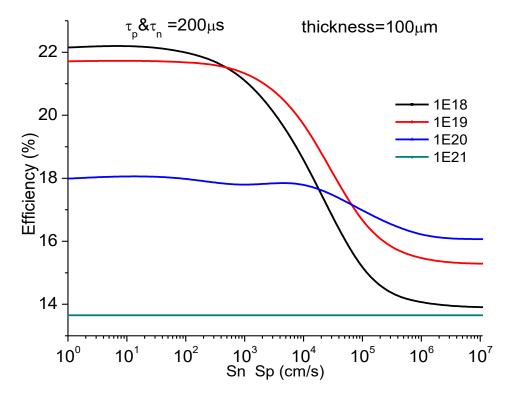

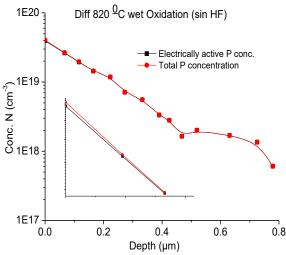

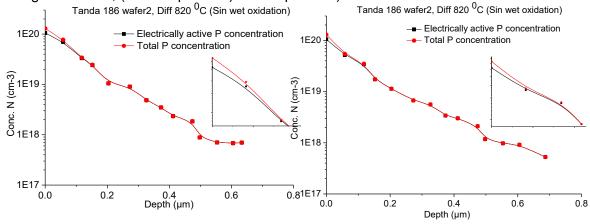

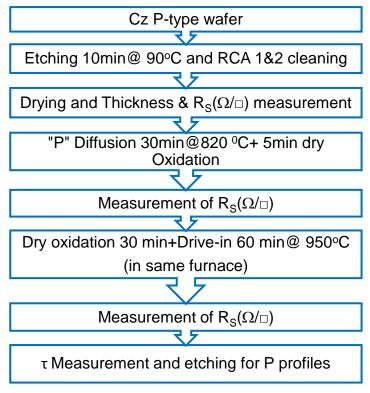

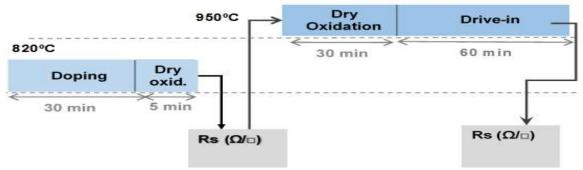

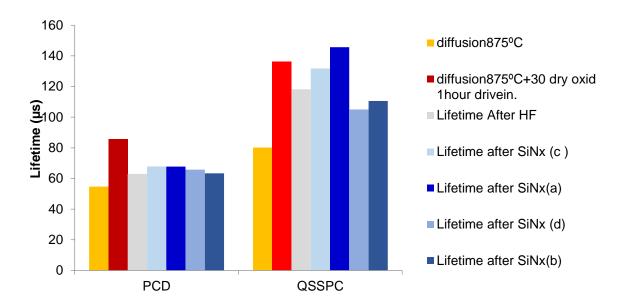

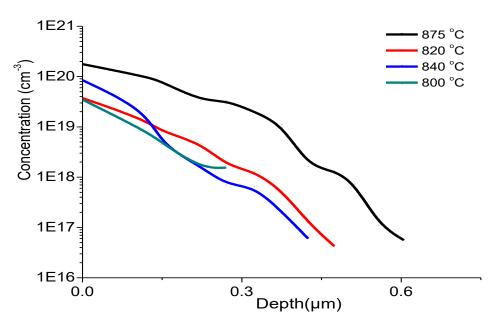

Due to low efficiency and poor quality of emitter's passivation, we have planned to investigate P diffusion deeply in order to get softly doped and passivated deep emitters. We have performed several phosphorus diffusion experiments at four temperatures ranging from 800 °C to 875 °C in order to get softly doped and deep  $n^+$ emitters and their profiles. The emitter saturation current density which limits the open circuit voltage depends on active phosphorus concentration and junction depth. Due to high temperature, P diffusion form dead layer which increased recombination and decrease overall cell efficiency. Dry or/and wet oxidation step with drive-in is introduced to minimize the effect of dead layer. The percentage of electrically active P is calculated by Tsai Model. Our results show that with increase of temperature, concentration of electrically active P decrease and vice versa. Our goal of this investigation was to make a single step diffusion process in a furnace for idustrial fabrication of solar cells.

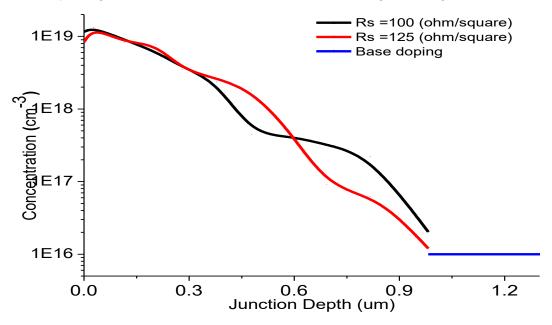

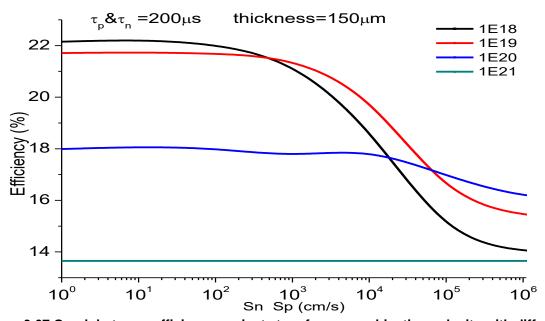

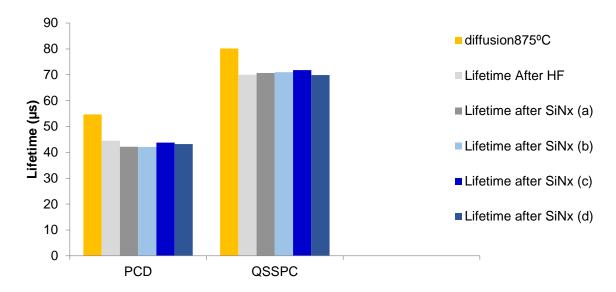

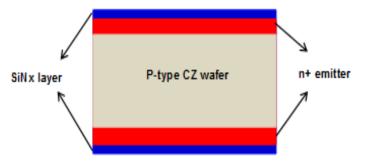

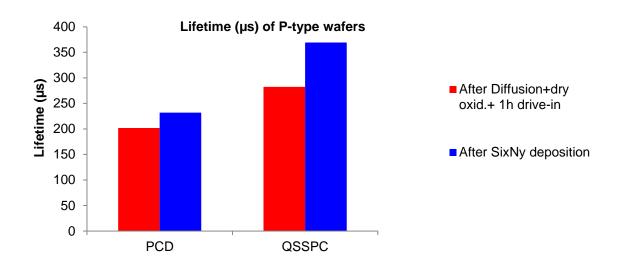

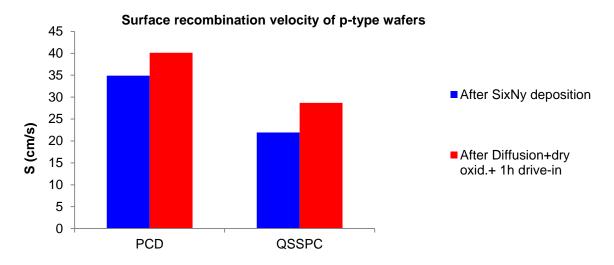

Reliability of emitters were evaluated by the influence of passivation. For each emitter surface conditions, surface recombination velocities have been simulated by PC1D for conventional emitters with 0.2  $\mu$ m junction depth and current emitters with 0.7  $\mu$ m depth which show that deep emitters junction depth give low values of emitter saturation current density (Joe) as compare to conventional junction depth. Emitters obtained by single thermal step are in range of 7-8 x10<sup>19</sup> cm<sup>-3</sup> with sheet resistance ~60  $\Omega$ / $\Box$  and junction depth 0.71  $\mu$ m and emitter saturation current density was 130 fA/cm<sup>2</sup>. In single step diffusion process the gettering is higher than conventional process and thermal budget is also low. In case of P-type material, we have measured lifetime around 200  $\mu$ s at high resistivity (5.4 $\Omega$ .cm) wafers and on N-type low resistivity (0.8  $\Omega$ .cm) wafers around 505  $\mu$ s by PCD technique. Improvement in lifetime is much higher than conventional gettering processes.

By using optimized new SiNx recipe, the maximum lifetime which we measured on stack structure SiO<sub>2</sub>/SiNx for passivated emitter was 334  $\mu$ s by PCD technique (transient photo-conductance decay) and 780  $\mu$ s by QSSPC technique (quasi steady state photo-conductance decay) which corresponds to an effective surface recombination velocity (SRV) 10cm/s by QSSPC technique and 24cm/s by PCD technique for p-type wafers and on n-type wafers, the maximum lifetime which we measured was 1263 $\mu$ s by PCD technique and 2209  $\mu$ s by QSSPC technique which corresponds to an effective SRV 3.8 cm/s for QSSPC technique and 15cm/s by PCD technique. Emitter's saturation current density (Joe) further decreased due to passivation effect of SiNx, which were in range of 5E-14 to 2.5E-14 A/cm² (25-50fA/cm²) for p-types wafers.

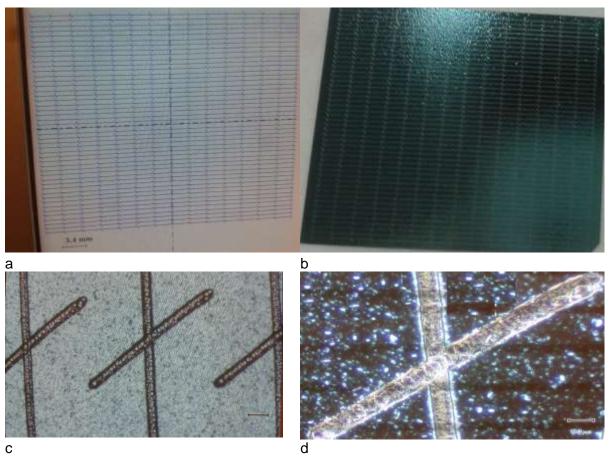

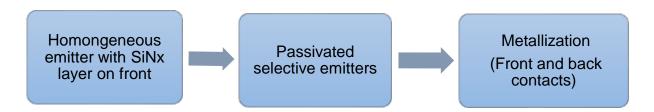

For softly doped emitters (sheet resistance  $100\text{-}200\,\Omega/sq$ ), it is difficult to make a contacts between front metal and softly doped emitters. This issue can be overcome by fabrication of selective emitters. Selective emitter have high doping concentration under metal contacts grid and low doping concentration under illumination area. Second P diffusion (back to back) was carried out at 875 °C for 30 minutes in laser scribed grooves area by protecting back surface and rest of front surface area with SiNx layer to create selective emitters. A thick layer of aluminum was deposited on backside of cells by screen printing technique in order create back surface field (BSF) as well as back contact. Optimal temperature for Al-deposition is 925 °C at 60inches/min belt furnace speed for good firing and contacts. In this step, rear surface Al-BSF with silicon oxide (SiO<sub>2</sub>) surface give highest open circuit voltage and lower Joe value.

After back contacts formation, we have measured *Sun-Voc* of cells to get electrical parameters of solar cells, we have found that emitter saturation current density (Joe) of cells increased which were in range from 6.45E-13 to 3.1E-12A/cm² and shunt conductance was in range from 2E-4 to 3.5E-3 ohm.cm². This Joe is due to rear emitters (AI-BSF), we have to optimize some parameters for appropriate metallization such as metallization paste in order to measure the real values (low) Joe of the cells. Quality of selective emitters is affected by chemical treatment, this phenomena was observed after lifetime measurements of selective emitters, we have found reduction in lifetime, what we had measured after SiNx layer deposition but lifetime is maintained under homogenous softly doped area. Destruction of lifetime is reduced when we have used teflon bath for chemical treatment instead of metallic bath. NaOH or KOH is used to remove laser damages prior to second P diffusion. By using KOH, reduction in lifetime is minor than NaOH.

We have measured *Sun-Voc* around 624 mV for p-type high resistivity wafers and 626mV for n-type low resistivity wafers. Final behavior of P/Al solar cell is due to Al-BSF, it can be further improved and theoretically expected is around 650 mV. Process which is used to fabricate selective emitter is feasible to apply for industrial fabrication of P/Al silicon solar cells with selective emitters with expected efficiency around 20%.

#### Contents

| 1 | Improve           | ements in P/Al high efficiency technology, AlSi                                            | 3  |

|---|-------------------|--------------------------------------------------------------------------------------------|----|

|   | 1.1 Inti          | oduction                                                                                   | 3  |

|   | 1.2 Ob            | jective of thesis:                                                                         | 4  |

|   | 1.2.1             | Description of Work:                                                                       | 4  |

|   | 1.2.2             | Summary; Analysis of state of Art                                                          | 8  |

|   | 1.3 De            | scription of P/AI technology                                                               | 12 |

|   | 1.3.1             | Research objective:                                                                        | 13 |

|   | 1.3.2             | Task1: Lightly doped phosphorus emitters                                                   | 13 |

|   | 1.3.3             | Selective phosphorus emitter                                                               | 14 |

|   | 1.3.4             | Task2: Surface passivation                                                                 | 14 |

|   | 1.4 Re            | ferences:                                                                                  | 18 |

| 2 | Basic o           | f Solar Cell Physics                                                                       | 23 |

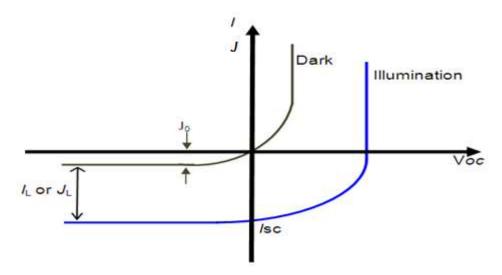

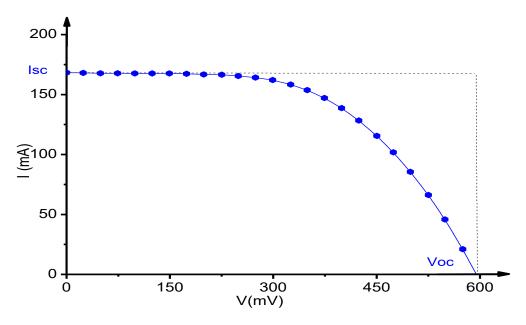

|   | 2.1 Cu            | rrent Voltage characterization                                                             | 23 |

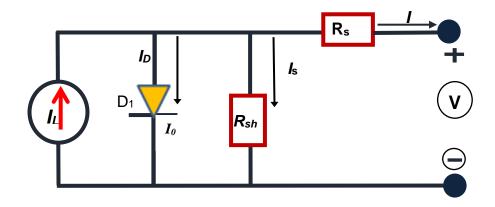

|   | 2.2 Eq            | uivalent circuit diode model of solar cell                                                 | 26 |

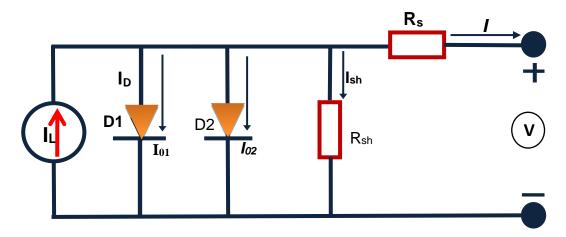

|   | 2.2.1             | Two Diode circuit model of solar cell                                                      | 28 |

|   | 2.2.2             | Measurement of IV curve under illumination                                                 | 29 |

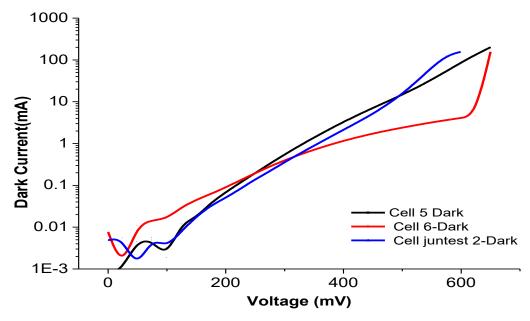

|   | 2.2.3             | Measurement of IV under dark and characteristics                                           | 30 |

|   | 2.2.4             | Limitation in two diodes Model                                                             | 33 |

|   | 2.3 Pa            | rasitic Resistance                                                                         | 33 |

|   | 2.3.1             | Series resistance and shunt resistance                                                     | 33 |

|   | 2.3.2             | Effect of temperature                                                                      | 34 |

|   | 2.3.3             | Short circuit current (Isc)                                                                | 35 |

|   | 2.3.4             | Open circuit voltage (Voc)                                                                 | 36 |

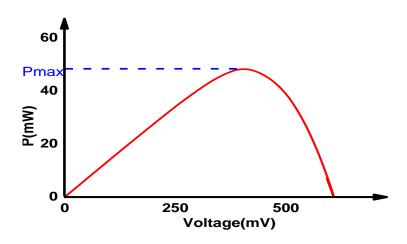

|   | 2.3.5             | Maximum power (P <i>max</i> )                                                              | 38 |

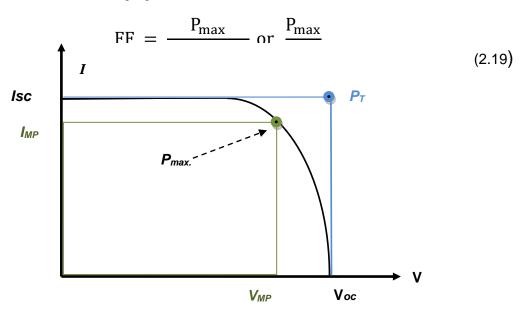

|   | 2.3.6             | Fill Factor (FF)                                                                           | 39 |

|   | 2.3.7             | Efficiency                                                                                 | 39 |

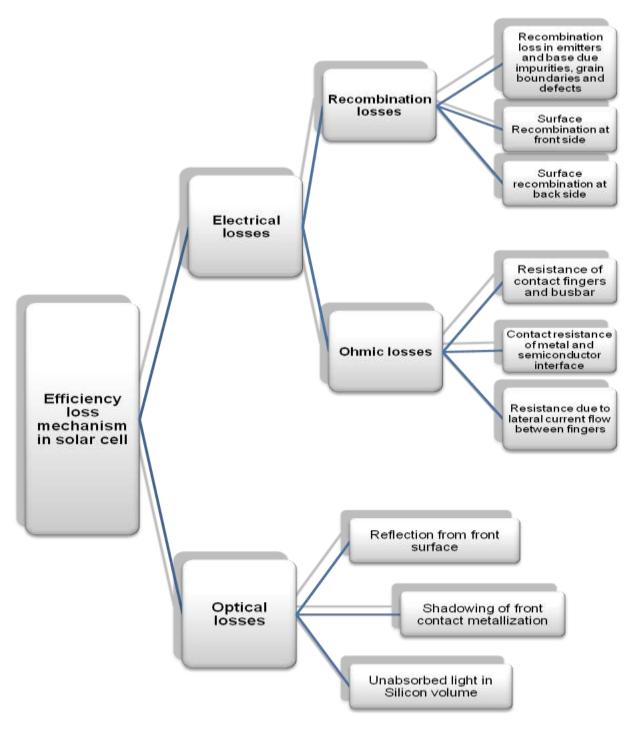

|   | 2.3.8             | Efficiency losses in Solar cell                                                            | 40 |

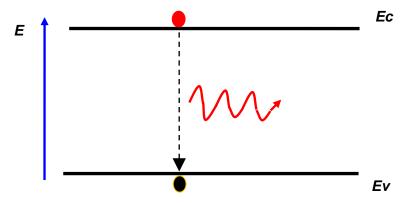

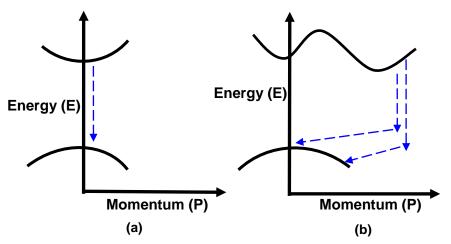

|   | 2.3.9             | Radiative Recombination (band to band recombination)                                       | 43 |

|   | 2.3.10            | Auger Recombination                                                                        | 44 |

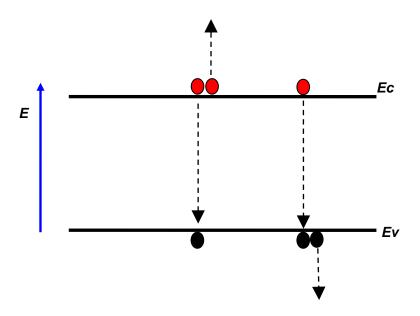

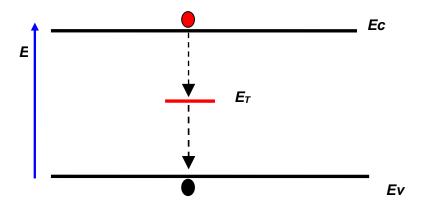

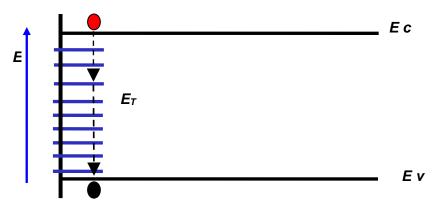

|   | 2.3.11<br>semicor | Shockley Read Hall recombination SRH (Recombination via defects states in ductor band gap) | 46 |

|   | 2.4 Su            | face recombination                                                                         | 48 |

|   | 2.4.1             | Minimization of Recombination                                                              | 50 |

|   | 2.4.2             | Surface passivation techniques                                                             | 50 |

|   | 2.4.3             | Front surface passivation                                                                  | 51 |

|   | 2.4.4             | Back surface passivation                                                                   | 51 |

|   | 2.4.5             | Bulk passivation                                                                           | 53 |

|   | 2.4.6             | Bulk passivation: The Gettering                                                            | 53 |

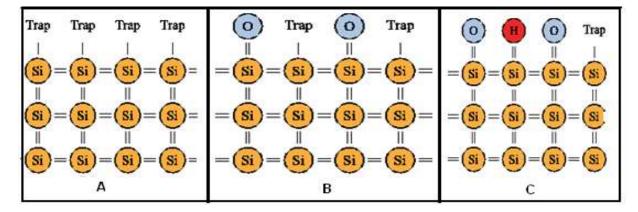

|   | 2.4.7             | Bulk passivation: Hydrogenation                                                            | 53 |

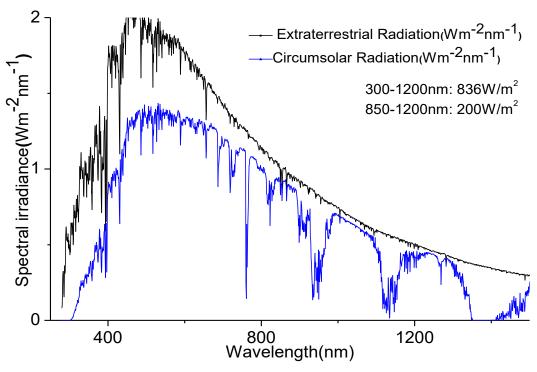

|                | 2.5   | Opt             | ical losses in solar cell                                            | 53  |

|----------------|-------|-----------------|----------------------------------------------------------------------|-----|

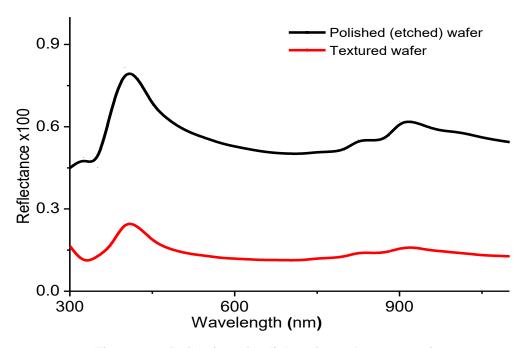

|                | 2.5.  | 1               | Front surface Reflection                                             | 54  |

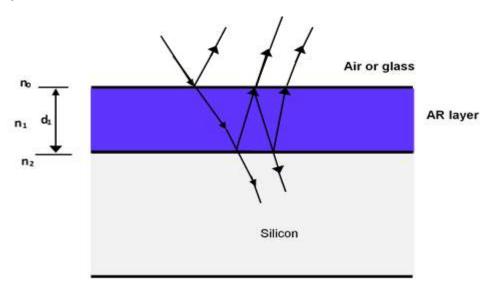

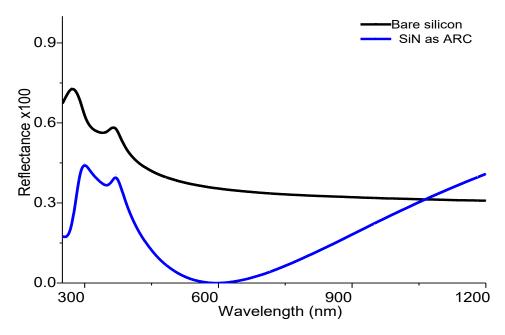

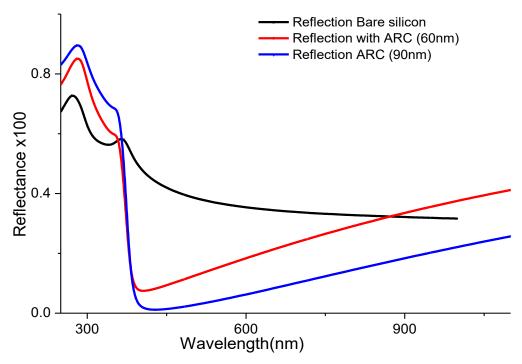

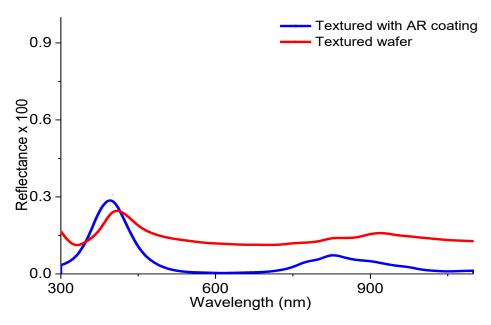

| 2.5.2<br>2.5.3 |       | 2               | Antireflection coatings                                              | 55  |

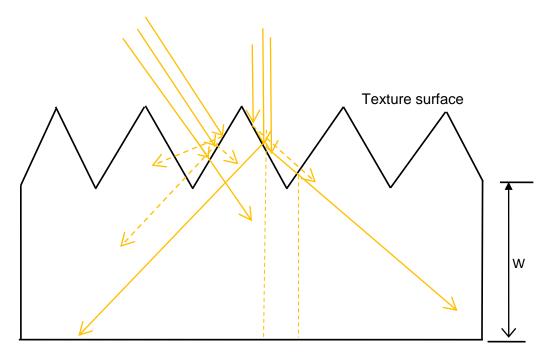

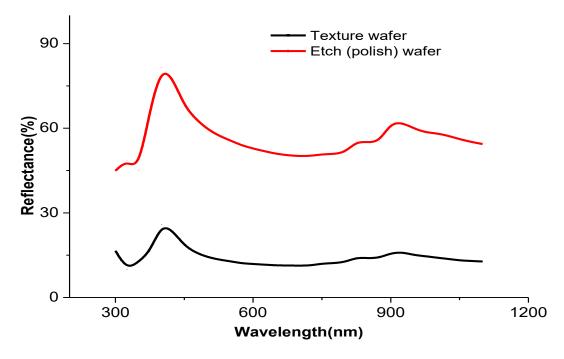

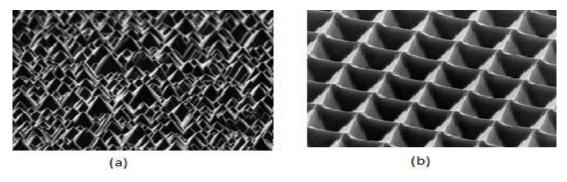

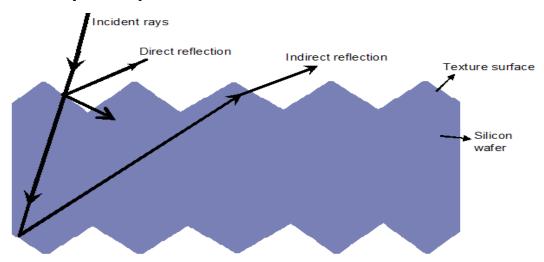

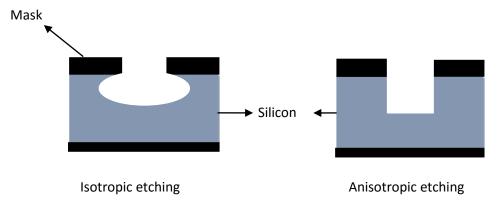

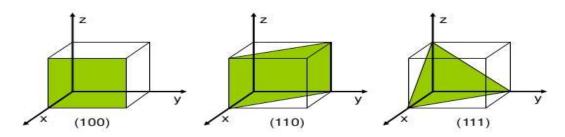

|                |       | 3               | Surface texturing                                                    | 57  |

|                | 2.5.4 | 4               | Parasitic absorption in ARC                                          | 59  |

|                | 2.5.  | 5               | Free carriers absorption (FCA)                                       | 60  |

|                | 2.5.0 | 6               | Rear Reflectance/Absorption                                          | 60  |

|                | 2.6   | Ref             | erences                                                              | 62  |

| 3              | Fab   | ricat           | ion of P/Al solar cells                                              | 69  |

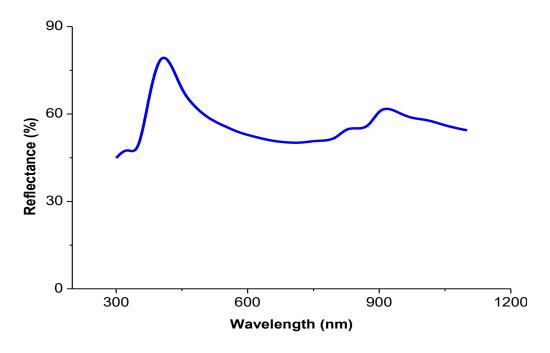

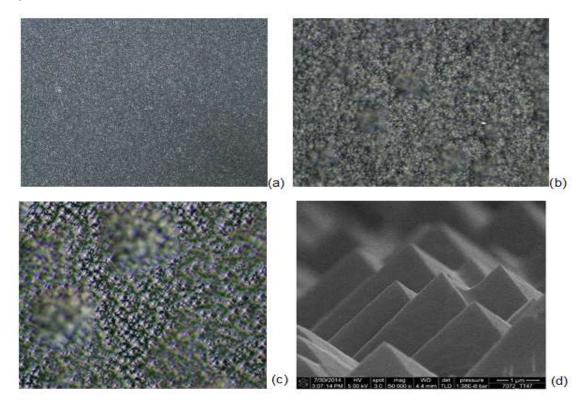

|                | 3.1   | Tex             | turization of Silicon wafers                                         | 72  |

|                | 3.1.  | 1               | Texturing Recipe (TIM recipe)                                        | 73  |

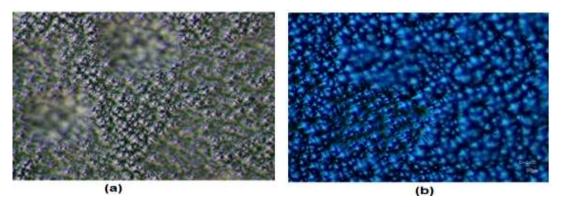

|                | 3.1.2 | 2               | Characterization of Texture wafers                                   | 73  |

|                | 3.2   | Wa              | fer cleanings (RCA1&2)                                               | 75  |

|                | 3.2.  | 1               | RCA1 chemicals recipe:                                               | 76  |

|                | 3.2.2 | 2               | RCA2 chemical recipe:                                                | 76  |

|                | 3.3   | Dop             | oing (Phosphorus diffusion)                                          | 76  |

|                | 3.3.  | 1               | Phosphorus pre-deposition (825 °C)                                   | 77  |

|                | 3.4   | She             | eet resistance and emitter characterization                          | 79  |

|                | 3.5   | Alu             | minum Deposition (By PVD)                                            | 83  |

|                | 3.6   | P/A             | I Drive-in process                                                   | 85  |

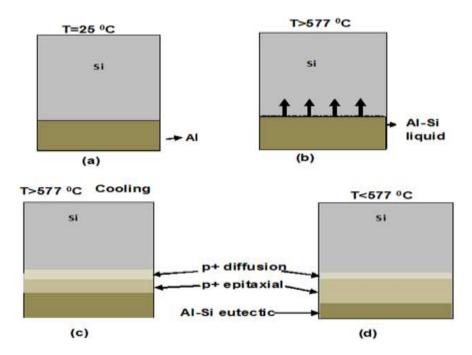

|                | 3.7   | Alu             | minum redistribution process (Redistribution of aluminum in silicon) | 85  |

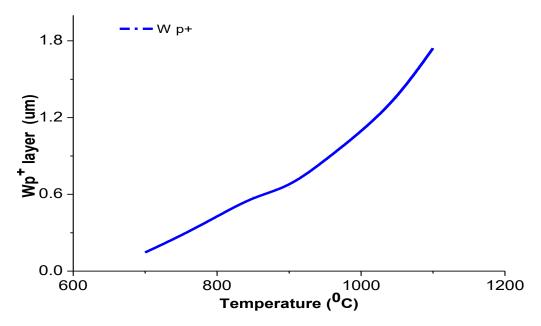

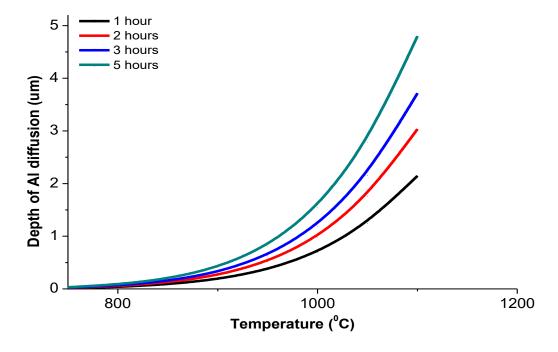

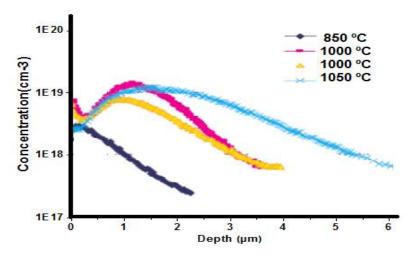

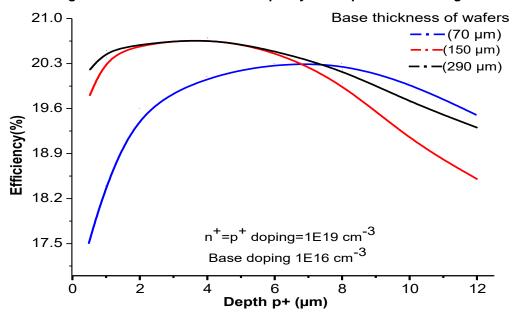

|                | 3.8   | PC <sup>2</sup> | 1D evaluation of p+ layer                                            |     |

|                | 3.8.  | 1               | Disadvantages of high temperature drive-in                           | 93  |

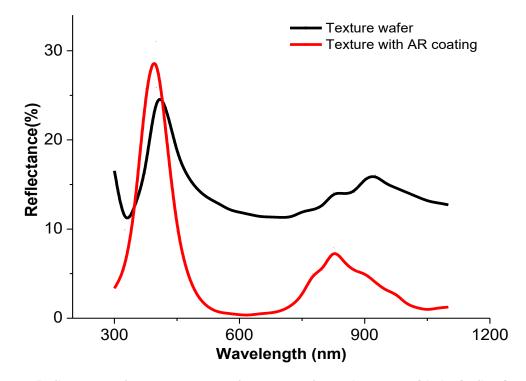

|                | 3.9   | Ant             | reflection coating (ARC)                                             | 94  |

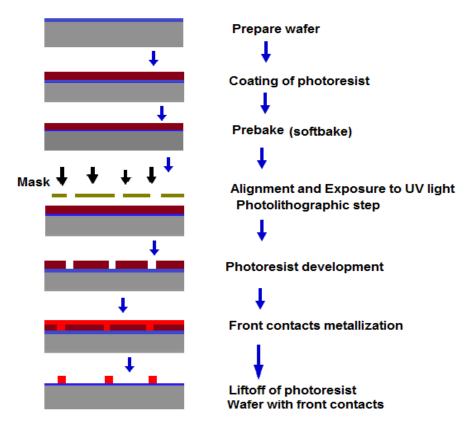

|                | 3.10  | Fro             | ntal metallization (By photolithography)                             | 96  |

|                | 3.10  | ).1             | Recommended coating conditions:                                      | 96  |

|                | 3.10  | ).2             | Photolithographic step (Expose to light)                             | 97  |

|                | 3.10  | 0.3             | Development of photoresist:                                          |     |

|                | 3.10  | ).4             | Liftoff of photoresist                                               | 98  |

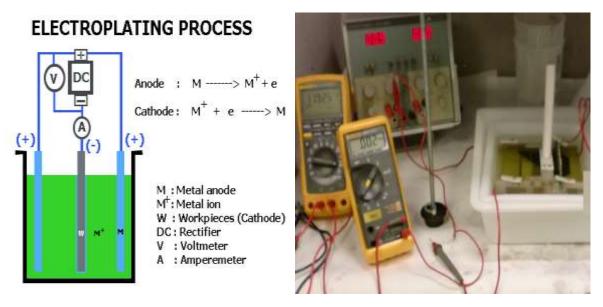

|                | 3.11  |                 | ctroplating or electro-deposition                                    | 100 |

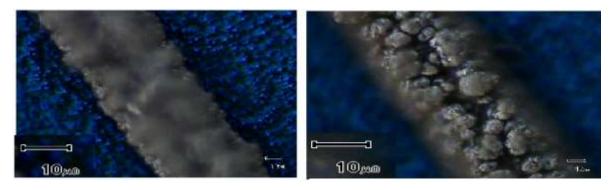

|                | 3.11  | .1              | Characterization of Electroplated cells                              | 101 |

|                | 3.11  |                 | Drawbacks:                                                           |     |

|                | 3.12  | Met             | allization (Back contacts)                                           | 102 |

|                | 3.13  |                 | ming gas annealing                                                   |     |

|                | 3.14  |                 | ation of solar cells by laser:                                       |     |

|                | 3.14  |                 | Laser Description:                                                   |     |

|                | 3.15  |                 | aracterization of P/AI solar cells                                   |     |

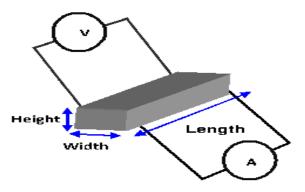

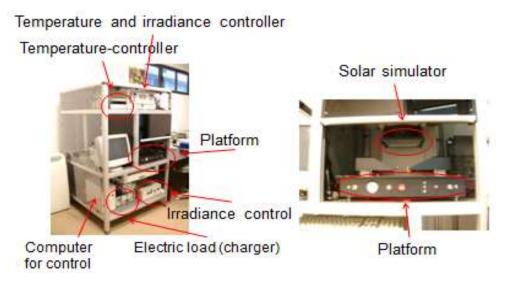

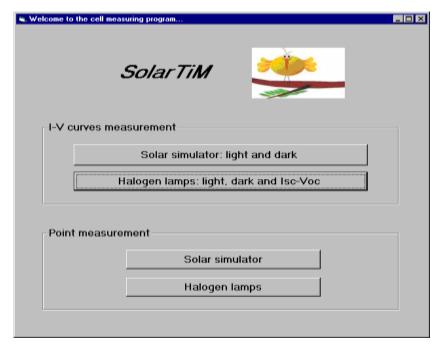

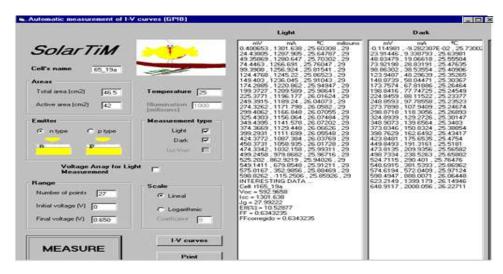

|                | 3.15  |                 | IV Curve measurement System                                          |     |

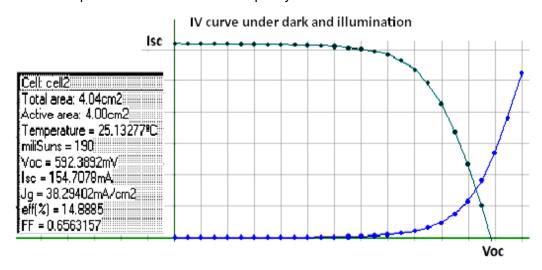

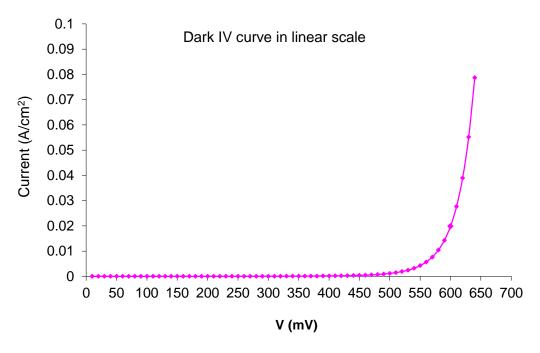

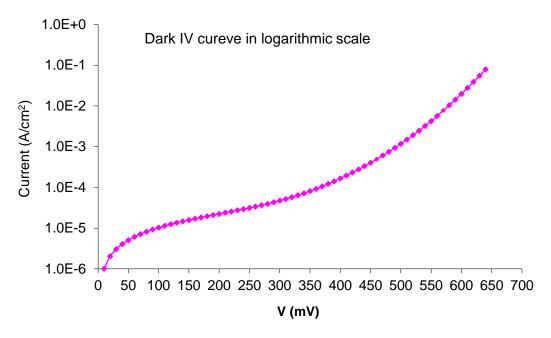

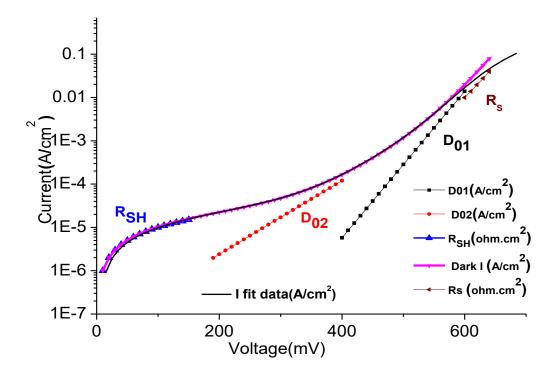

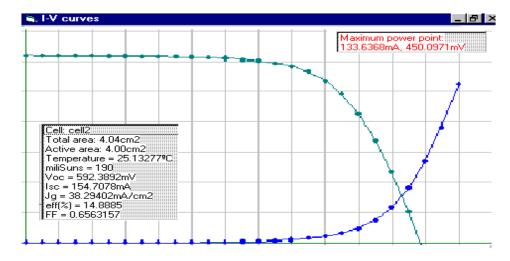

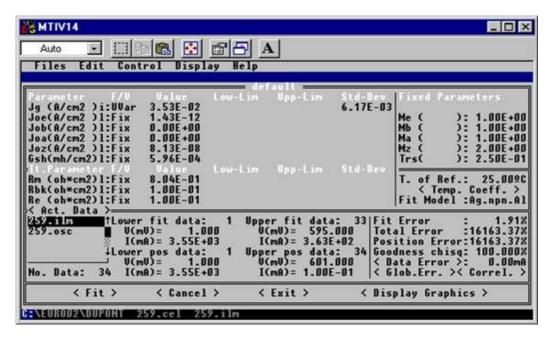

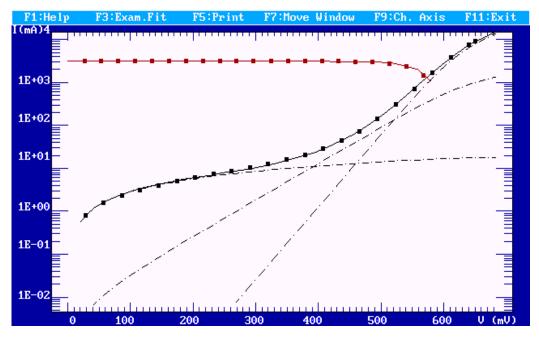

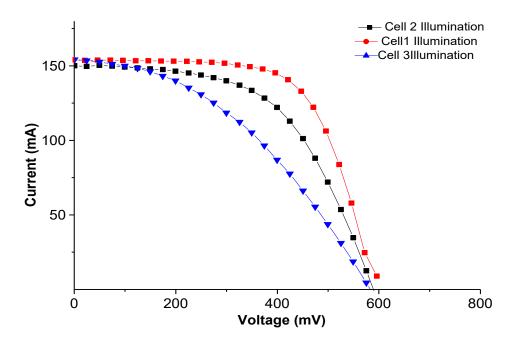

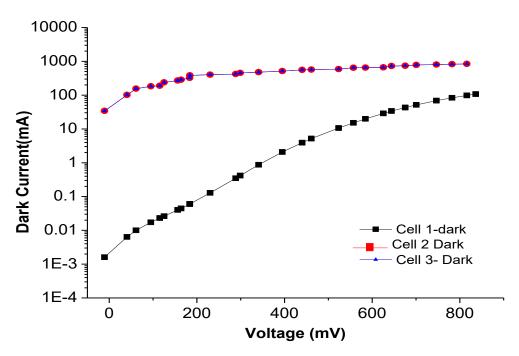

|                | 3.15  | 5.2             | I V curve measurements and characterization of solar cell (batch1)   | 109 |

|   | 3.1  | 5.3   | Sun-Voc Measurements and Characterization                                      | 111 |

|---|------|-------|--------------------------------------------------------------------------------|-----|

|   | 3.16 | Fab   | rication of silicon solar cell by P/Al technology (Batch 2)                    | 114 |

|   | 3.17 | IV c  | haracterization of P/AI solar cell of batch 2                                  | 114 |

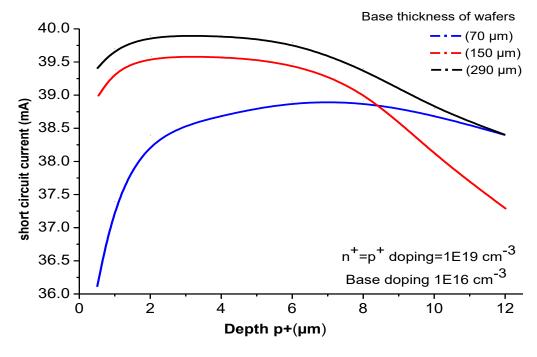

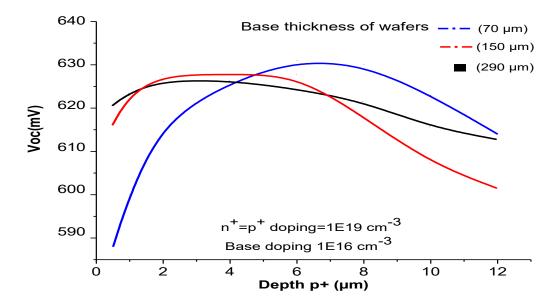

|   | 3.18 | Thi   | n silicon solar cells                                                          | 116 |

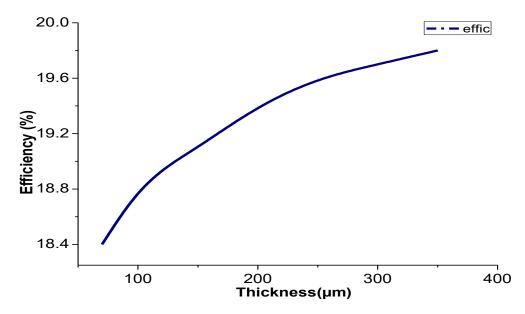

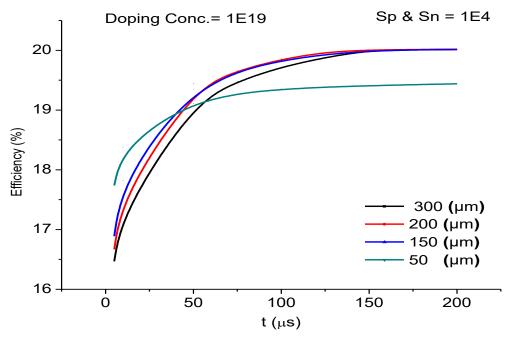

|   | 3.18 | 8.1   | Thinning effect of P/Al solar cell.                                            | 119 |

|   | 3.19 | Get   | tering process by Al and lifetime measurement of P/Al solar cells              | 122 |

|   | 3.20 | Cor   | clusion:                                                                       | 125 |

|   | 3.21 | Ref   | erences:                                                                       | 127 |

| 4 | Diff | fusio | n                                                                              | 135 |

|   | 4.1  | Dop   | ing:                                                                           | 135 |

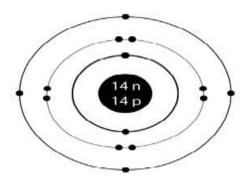

|   | 4.1. | .1    | N-type doping:                                                                 | 135 |

|   | 4.1. | .2    | P-type doping:                                                                 | 135 |

|   | 4.1. | .3    | Diffusion:                                                                     | 136 |

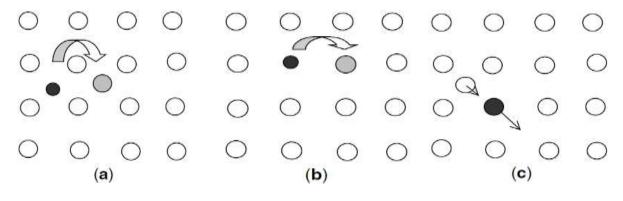

|   | 4.1. | .4    | Phosphorus diffusion:                                                          | 136 |

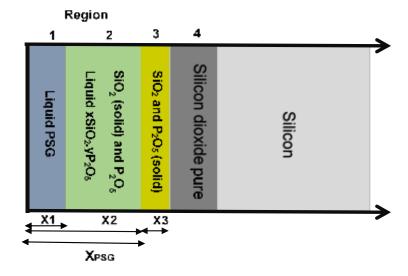

|   | 4.1. | .5    | PSG (Phosphorus Silicate Glass):                                               | 137 |

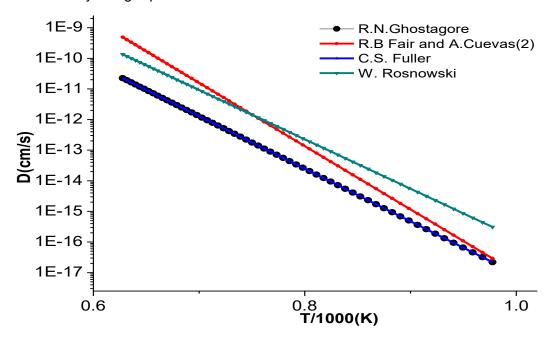

|   | 4.1. | .6    | Diffusivity of P in Si                                                         | 138 |

|   | 4.1. | .7    | Solid Solubility of P in Silicon:                                              | 141 |

|   | 4.2  | Obj   | ective of P diffusion:                                                         | 144 |

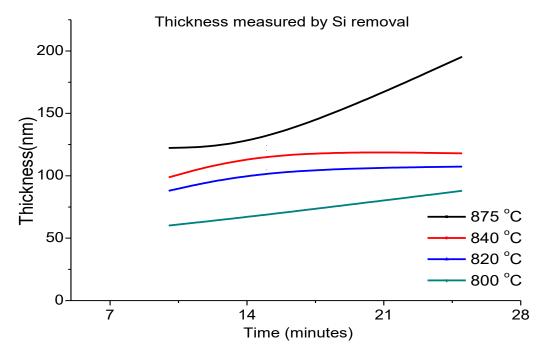

|   | 4.3  | Pho   | sphorus diffusion (800- 875°C)                                                 | 144 |

|   | 4.3  | .1    | Phosphorus Pre-deposition                                                      | 144 |

|   | 4.3. | .2    | Oxidation and drive in process                                                 | 146 |

|   | 4.4  | Oxi   | dation Process:                                                                | 147 |

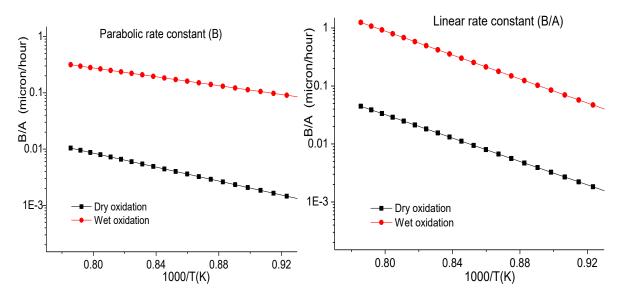

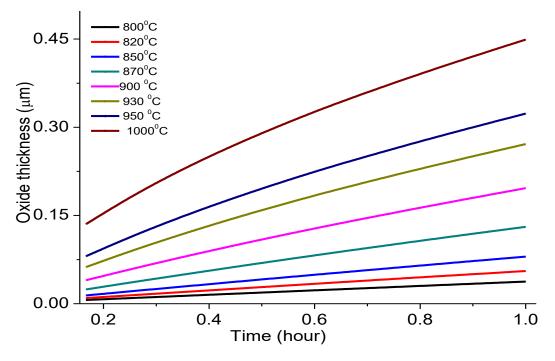

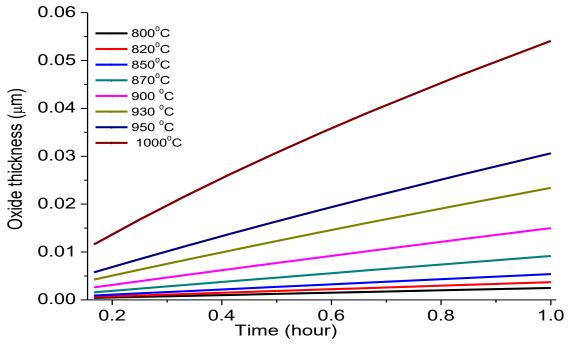

|   | 4.4. | .1    | Calculation for growth of silicon oxide in wet and dry oxidation               | 149 |

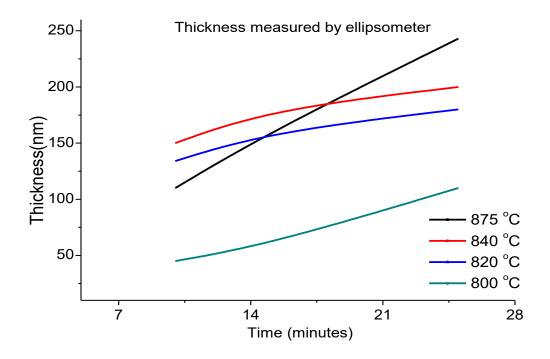

|   | 4.4. | .1.1  | Wet Oxidation                                                                  | 150 |

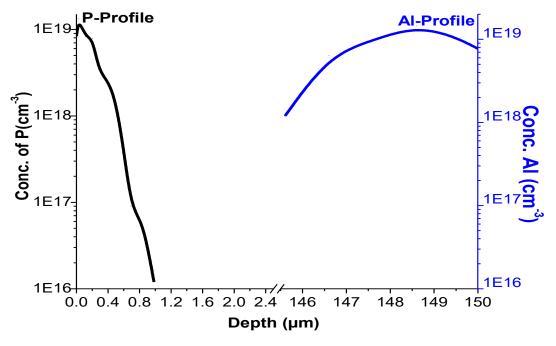

|   | 4.5  | Diff  | usion profiles                                                                 | 158 |

|   | 4.5  | .1    | Q calculation                                                                  | 162 |

|   | 4.6  | Tota  | al concentration of P diffusion                                                | 163 |

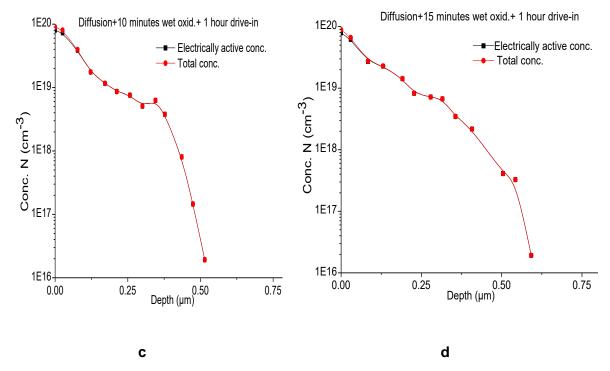

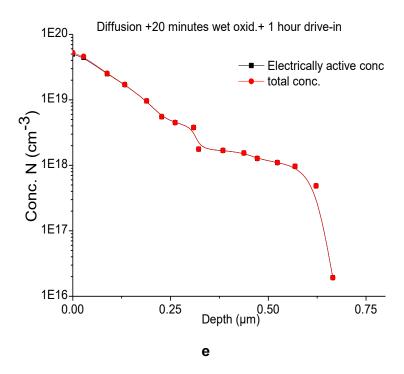

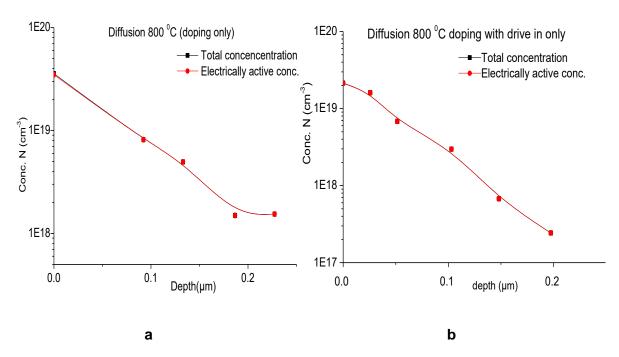

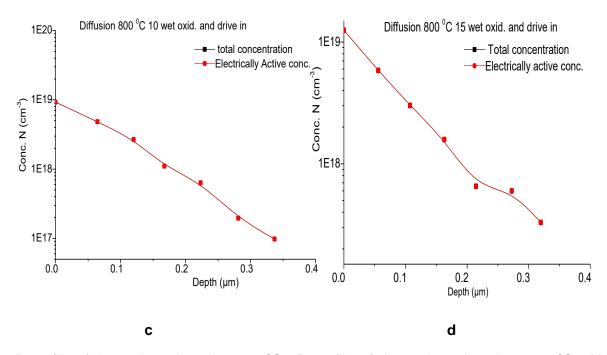

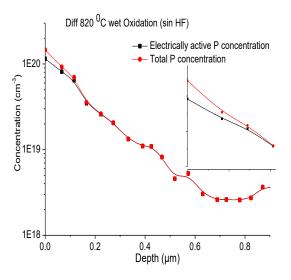

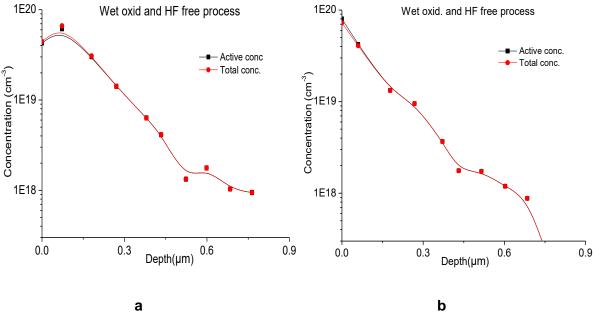

|   | 4.6  | .1    | Electrically active and total concentration of P diffusion profiles for 875 °C | 165 |

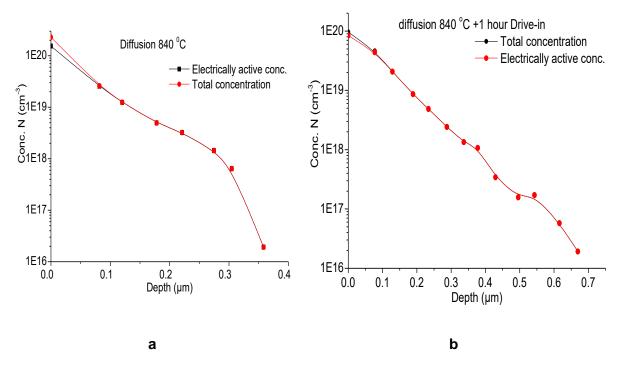

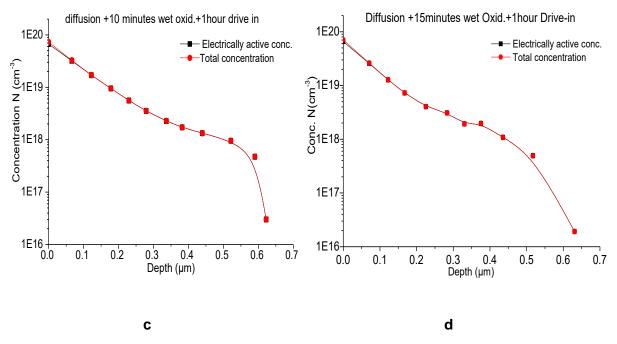

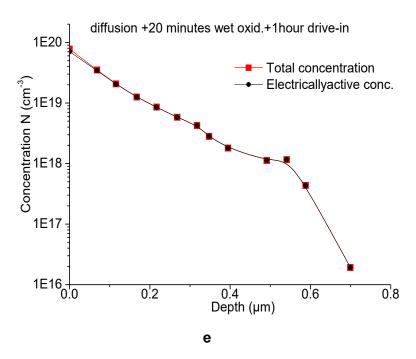

|   | 4.6  | .2    | Electrically active and total concentration of P diffusion profiles for 840 °C | 166 |

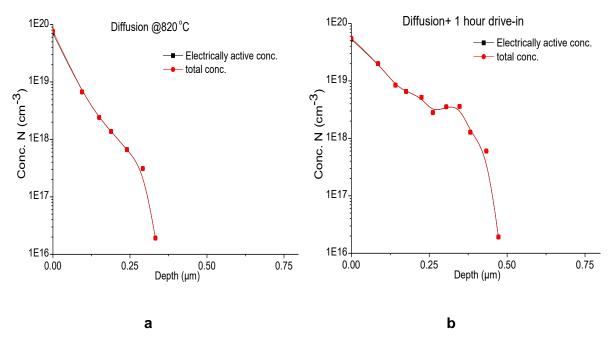

|   | 4.6  | .3    | Electrically active and total concentration of P diffusion profiles for 820 °C | 168 |

|   | 4.6  | .4    | Electrically active and total concentration of P diffusion profiles for 800 °C | 170 |

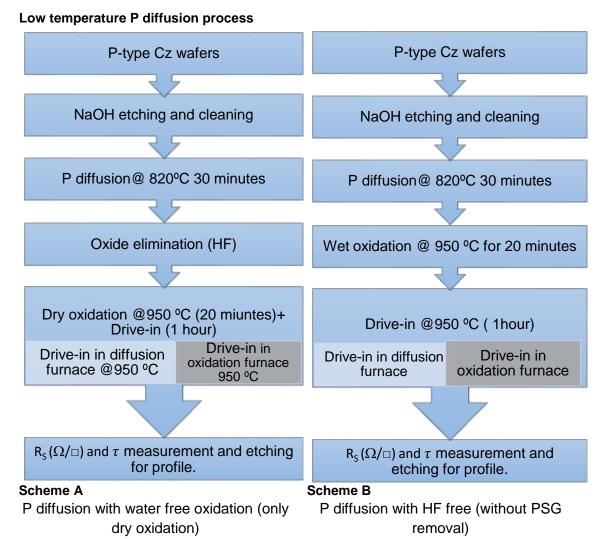

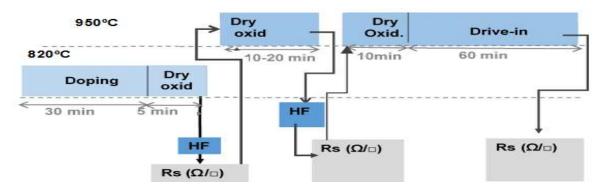

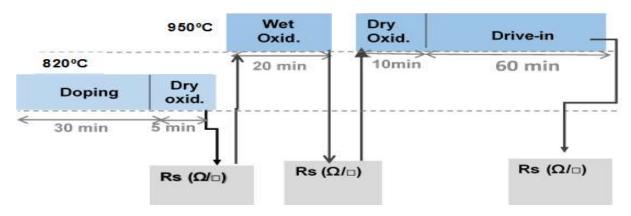

|   | 4.7  | Low   | Temperature Diffusions                                                         | 176 |

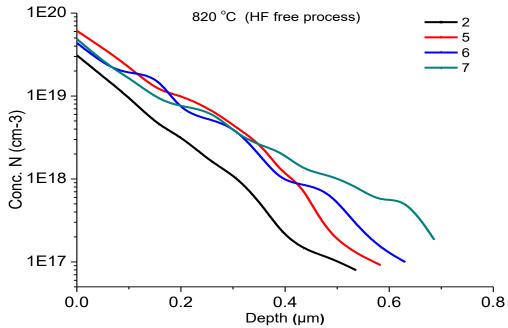

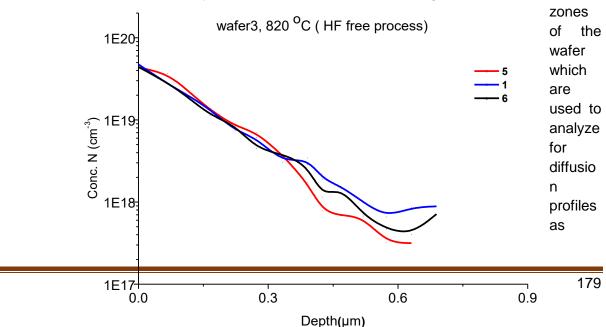

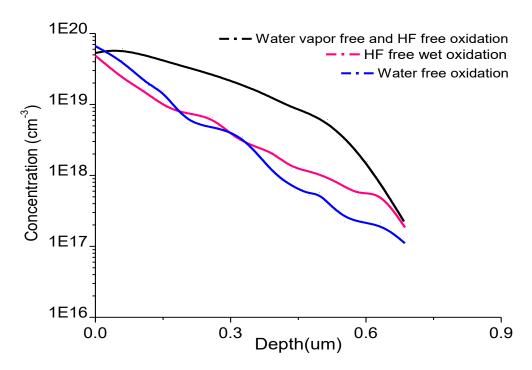

|   | 4.7  | .1    | Low temperature diffusion with HF free process                                 | 178 |

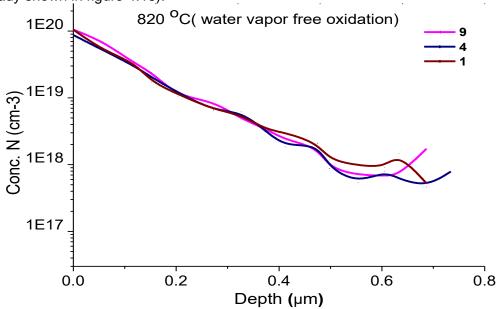

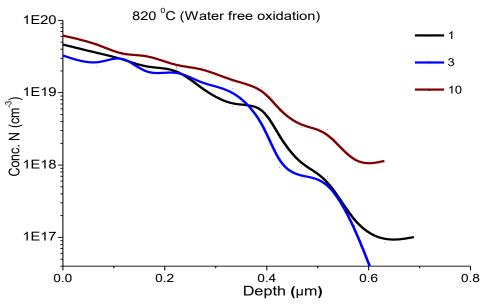

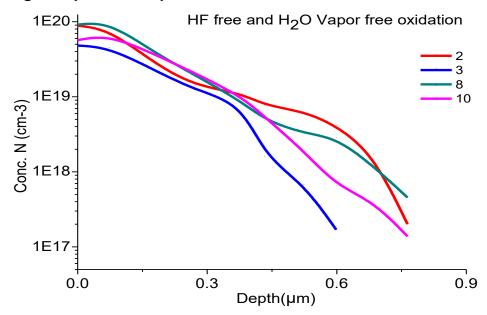

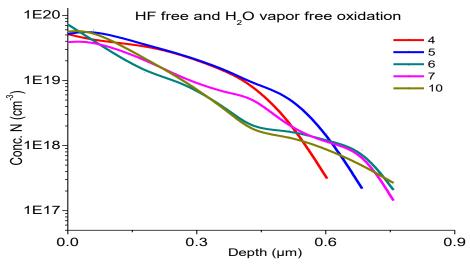

|   | 4.7  | .2    | Low temperature diffusion profiles of HF free process                          | 179 |

|   | 4.7  | .3    | Low temperature diffusion profile of water free process                        | 180 |

|   | 4.7  | .4    | Results of low temperature diffusion                                           | 181 |

|   | 4.8  | Sin   | gle step diffusion process (Industrial process)                                | 183 |

|   | 4.8  | .1    | Single step diffusion profiles                                                 | 184 |

|   | 4.8. | .2    | Summary of Low temperature diffusion                                           | 189 |

|   | 4.9                                             | Conclusion:                                                                                  |     |  |  |  |

|---|-------------------------------------------------|----------------------------------------------------------------------------------------------|-----|--|--|--|

|   | 4.10 References                                 |                                                                                              |     |  |  |  |

| 5 | Pass                                            | sivation and Selective Emitter Formation                                                     | 199 |  |  |  |

|   | 5.1                                             | Silicon passivation                                                                          | 199 |  |  |  |

|   | 5.2                                             | Deposition Techniques:                                                                       | 200 |  |  |  |

|   | 5.2.1                                           | Plasma Enhanced Chemical Vapor Deposition (PECVD):                                           | 201 |  |  |  |

|   | 5.2.2                                           | Silicon nitride (Si <sub>3</sub> N <sub>4</sub> ):                                           | 202 |  |  |  |

|   | 5.2.3                                           | Instrumental description                                                                     | 203 |  |  |  |

|   | 5.3                                             | Surface passivation:                                                                         | 203 |  |  |  |

|   | 5.4                                             | The Lifetime Measurements                                                                    | 204 |  |  |  |

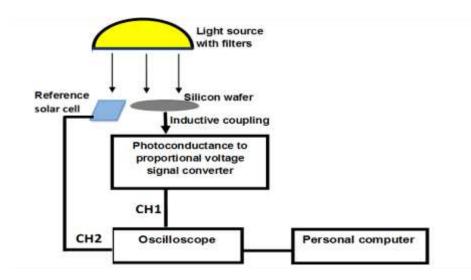

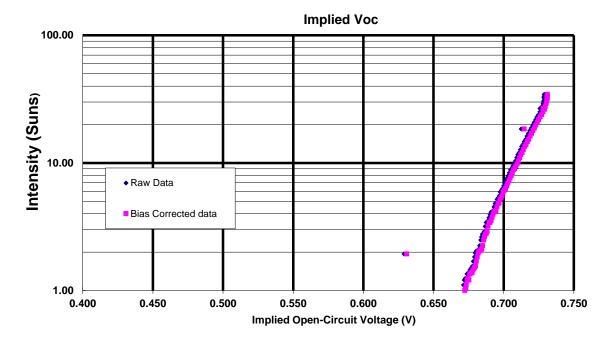

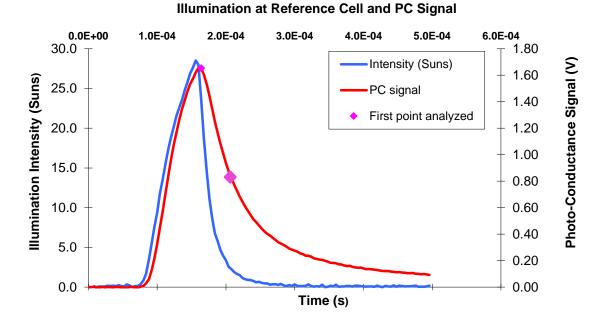

|   | 5.4.1                                           | QSSPC technique                                                                              | 205 |  |  |  |

|   | 5.4.2                                           | QSSPC and surface recombination                                                              | 206 |  |  |  |

|   | 5.4.3                                           | Transient photo conductance                                                                  | 209 |  |  |  |

|   | 5.5                                             | Passivation through oxidation Process                                                        | 210 |  |  |  |

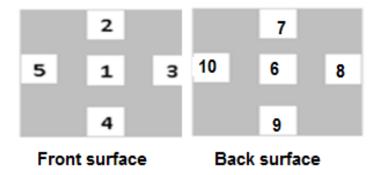

|   | 5.5.1                                           | Results and characterization passivated surface                                              | 212 |  |  |  |

|   | 5.6                                             | Passivation with stoichiometric SiNx Deposition (N-type wafer)                               | 213 |  |  |  |

|   | 5.6.1                                           | Objective:                                                                                   | 213 |  |  |  |

|   | 5.6.2                                           | Experimental procedure:                                                                      | 213 |  |  |  |

|   | 5.6.3                                           | Recipe of silicon nitride (SiNx) deposition                                                  | 214 |  |  |  |

|   | 5.7                                             | Passivation of emitter (N-type wafers)                                                       | 218 |  |  |  |

|   | 5.7.1                                           | Passivation of softly doped and high doped emitters (N-type substrate)                       | 220 |  |  |  |

|   | 5.8                                             | Passivation of Softly doped emitters on P-type substrate                                     | 225 |  |  |  |

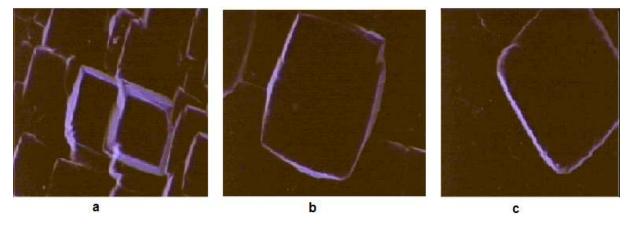

|   | 5.9                                             | Selective emitters                                                                           | 227 |  |  |  |

|   | 5.9.1                                           | Fabrication of selective emitters                                                            | 228 |  |  |  |

|   | 5.9.2                                           | Selective emitter formation                                                                  | 234 |  |  |  |

|   | 5.9.3                                           | Selective emitter's formation on n-type wafers                                               | 238 |  |  |  |

|   | 5.10                                            | Selective emitter's formation (P-type wafers)                                                | 241 |  |  |  |

|   | 5.11                                            | Aluminum optimization and Al-BSF                                                             | 246 |  |  |  |

|   | 5.12                                            | Conclusion:                                                                                  | 249 |  |  |  |

|   | 5.13                                            | References:                                                                                  | 251 |  |  |  |

| 6 | Con                                             | clusion and future plan                                                                      | 259 |  |  |  |

|   | 6.1                                             | Conclusion:                                                                                  | 259 |  |  |  |

|   | 6.2                                             | Future Plan:                                                                                 | 265 |  |  |  |

| Α | ppendi                                          | (es                                                                                          | 267 |  |  |  |

| Α | ppendix                                         | A:                                                                                           | 269 |  |  |  |

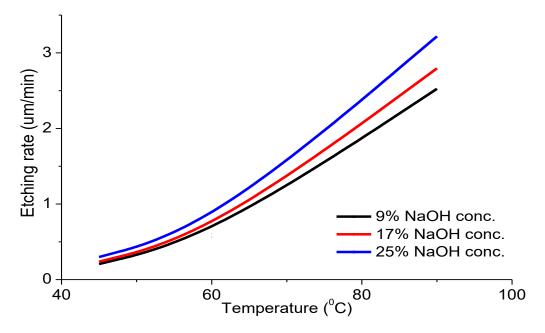

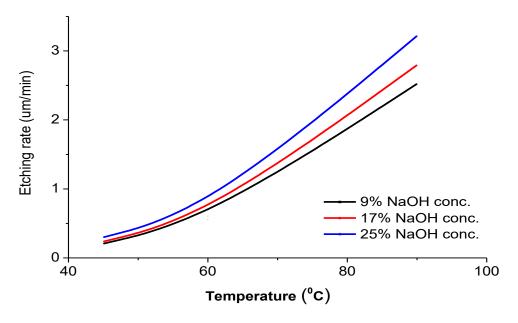

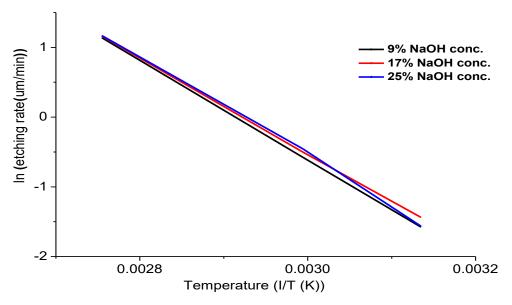

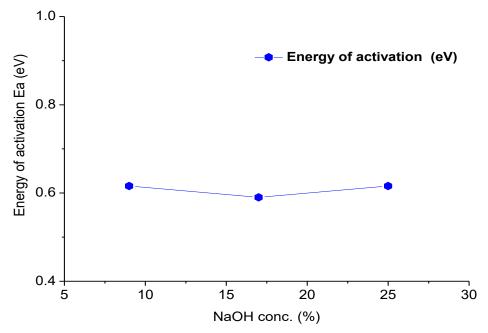

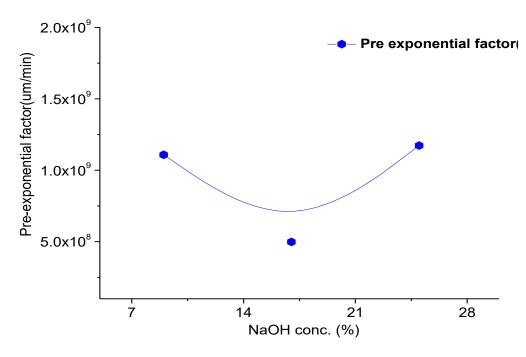

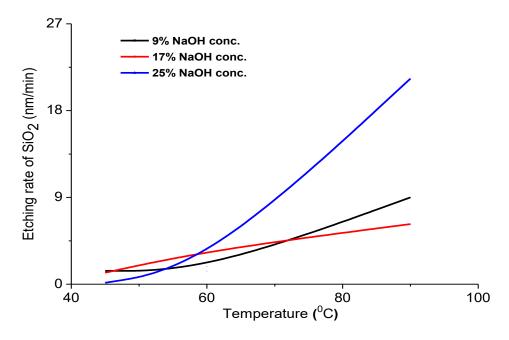

|   | -                                               | naracteristics of sodium hydroxide (NaOH) for silicon, silicon dioxide and silicon nit plots |     |  |  |  |

| Α | Appendix A1: Etching rate of silicon            |                                                                                              |     |  |  |  |

| Α | Appendix A2: Etching rate of silicon dioxide276 |                                                                                              |     |  |  |  |

| Δ | nnendix                                         | A3: Etching rate of silicon nitride                                                          | 278 |  |  |  |

| Appendix B                 | 282 |

|----------------------------|-----|

| List of abbreviations used | 283 |

| Publications               | 285 |

## Chapter 1

# 1 Improvements in P/AI high efficiency technology, AISi

#### 1.1 Introduction

With the increase of human population, energy demand is also increasing steadily and rapidly. The conventional energy resources such as fossil and nuclear fuels are limited and associated with negative effect on environment, such as greenhouse gases effect, holes in ozone layer, acid rain and pollution cannot be neglected. Therefore new means of energy is necessary which should be renewable and environmental friendly.

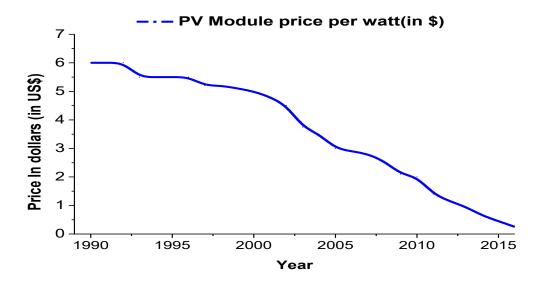

Today conversion of sunlight into electricity by using photovoltaics is attractive, environmental friendly way to produce renewable energy. Photovoltaics systems especially in case of silicon solar cell raw material is available in abundant in nature, can be used everywhere in world and almost maintenance free flexible scale from milli-watt to megawatt. Due to these advantages, PV competes with conventional energy production but cost of PV electricity is still higher as compared to conventional resource of electricity. The aim of this research work is increase competitiveness of photovoltaics by improving the technology for high efficiency process and decreasing cost. The cost of solar cell modules is at this time is around 0.6\$/Wp, this cost can be reduced to below 0.3\$/Wp. Major tasks in solar cell research are;

- · Reduce material and fabrication costs

- Improve technology

- Improved efficiencies

- Industrial application for high volume of production (≥ 500 MWp/year) [1].

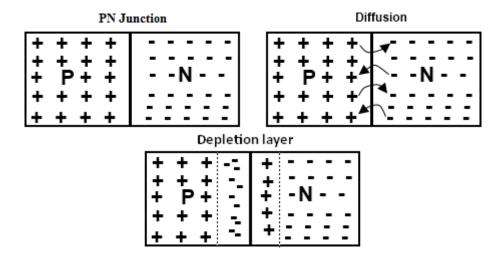

Photovoltaic cell or photoelectric cell is a solid state electrical device that converts the sun light energy directly into electrical energy by the photoelectric effect. Photovoltaic is the field of technology and research related to the practical application of photovoltaic cells in producing electricity from light. After petrol crisis and the emissions problems deriving from the use of petrol derivatives, solar cells and other alternative sources of energy gained important place in the application of alternative energy. It has been under intensive investigation for cost-effective photovoltaics, since the development of the first solar cells in the 1950s [2-4]. The materials currently used for the fabrication of photovoltaic solar cells included crystalline materials are in the form of mono and polycrystalline silicon, amorphous silicon, cadmium telluride, and copper indium selenide/sulfide. Recently available solar cells are fabricated from bulk materials, in which wafers are cut into 150-300 µm thickness, and processed to fabricate solar cells like other semiconductors. Second group of solar cells, which are used as thin film layers are organic dyes and organic polymers that are deposited on substrate. A third group of cells are fabricated from nanocrystals, which is also called quantum dots or nanoparticles. Silicon remains the only material which is deeply investigated in both bulk and thin film forms of solar cell. Among all alternative technologies to silicon-based PN-junction solar cells, could lead the most significant cost reduction. [5]

#### 1.2 Objective of thesis:

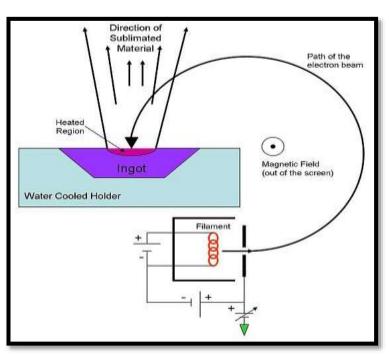

The main objective of this work is to develop high efficiency technology for solar cells which are industrializable exceed the efficiency and thickness estimation provided by industry. High efficiency technology, P/AI technology has shown efficiency 19% on float-zone wafer [6]. This technology consists of lightly doped phosphorus emitters of  $100-150\Omega$ /square, Aluminum evaporated by electron beam machine, diffused in quartz furnace and contacts are defined by metals evaporation by using photolithographic technique and lift-off. In this work, this technology is applied on monocrystalline silicon wafers, obtained by Czochralski growth (CZ), a low quality wafers than float-zone wafers. This technology will be compatible with 150  $\mu$ m thickness and it is based on phosphorus and aluminum diffusion on p-type silicon wafers (Cz) with expected efficiencies over 18% [7-8].

The proposed work not only contributes to sustainable development but also direct impact on effective solution of environmental protection. In addition to this, the work aim is to improve P/AI solar cell technology for high efficiency, which can be implemented in industry. It is well recognized that the efficiency of photovoltaic systems is the key and to shorten the time is fully competitive. The proposed work not only contributes to sustainable development but also direct impact on effective solution of environmental protection.

Although the efficiencies achievement is remarkable and next step will be to transfer this technology from laboratory to industry in the future. Optimization analysis of phosphorus emitters is key step of this technology in order to maintain high efficiency. Phosphorus emitters are necessarily to be a selective, for this purpose P diffusion is investigated deeply to get lightly doped emitters under illumination area and highly doped under the metallization grid. Passivation can be achieved through layers of silicon nitride with silicon oxide, which also act as antireflection layers. For optimization of aluminum diffusion, some parameters are taken into account such as the amount of deposition of metal, temperature, process time, and composition of environment in the furnace to improve the lifetime and passivation. Techniques developed during this work under specific tasks (selective phosphorus emitter, aluminum BSF (back surface field), and metallization with photolithography by using electron beam (laboratory technique) and screen-printing or ink-jet (industrial technique), edge insolation of devices (solar cell) through laser), applied in fabrication of P/Al cells on Cz silicon wafers and expected efficiency is close to 18%.

#### 1.2.1 Description of Work:

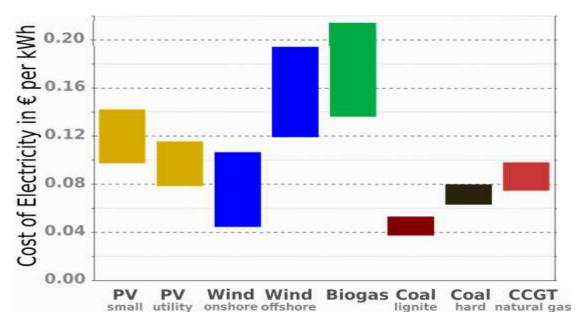

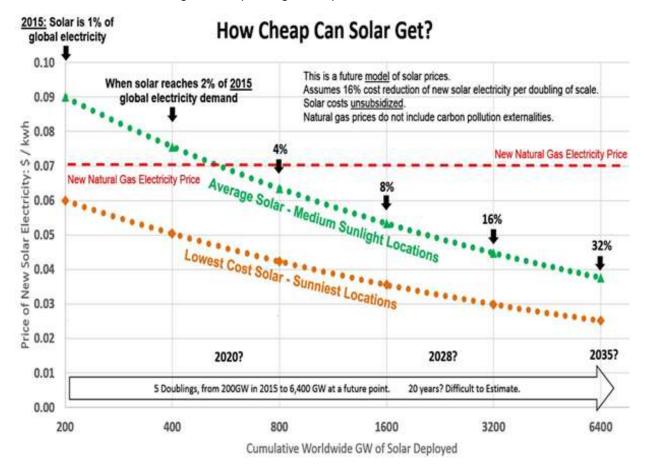

Photovoltaic solar energy is one kind of renewable energy source, it is started to develop from 1970 as an alternative resource of electricity. It is providing electricity but its efficiency and cost has not yet met the expectations what we have now a days. Solar energy has great advantages associated with its unlimited and widely distributed as fuel in the form of sun light. With respect to cost solar energy is still expensive. According to current estimation as shown in figure 1.1, average cost of solar energy for is ranging from 0.08-0.14€/kWh in European Union while in European Union average cost of electricity for end user is 0.05-0.10€/kWh. However we can see the cost reduction in recent years. By the using advance technology and improved technology, it could be cheaper [2].

Figure 1.1 Cost of electricity from different resources in € Per KWh (source: Fraunhofer ISE)

Today investigation in solar energy is an area of undeniable interest. On one hand, it is necessary to find new alternative energy resource and other hand we are interested to find clean energy pollution free energy.

- There are many opinions about production of petroleum products and fossil fuel. It is thought that energy resources will be gradually decreased in near future. In 2008 price of petroleum reached as high as 148\$/barrel and followed by a fluctuation in the following months. Currently prices of petroleum are very unstable. Natural gas is also evolved in similar way. The European Union is mainly depending on fossil fuel, it is necessary for diversification of energy sources in order to avoid the worsening the economic crisis.

- Second is the uneven distribution of energy resources, which are currently concentrated in small area of Middle East, whose political situation is uncertain. In contrary solar energy is abundant and cannot be monopolized by any country.

- In the mid of June 2009 EU directive force on "Promoting the use of energy from renewable resources" which aims was to reduces emissions of greenhouse gases by 20% in 2020 (Pollution free energy).

- In order to solve above mentioned problems, renewable energies are the best candidate to overcome the major problem of energy supply and climate changes. The renewable energy resources which come from external resources usually from sun do not run out, in contrast to conventional energy resources based on fossil fuel in form of carbon, petrol and gas. There are many energy resources such as wind, geothermal biomass, hydrodynamic and solar energy. All of these form of energy resources capable of producing huge quantity of electricity for present and future use. There are strong reasons to use renewable energy which are as follow:

- These resources are environmental friendly in nature; do not contribute to produce carbon dioxide or other greenhouses gases.

- These energy resources are everlasting abundance and widely distributed.

• Renewable energy resources can supply energetically to poor areas/countries, avoiding energy dependence on other countries.

Among them, photovoltaic solar energy is the best positioned to face for long term.

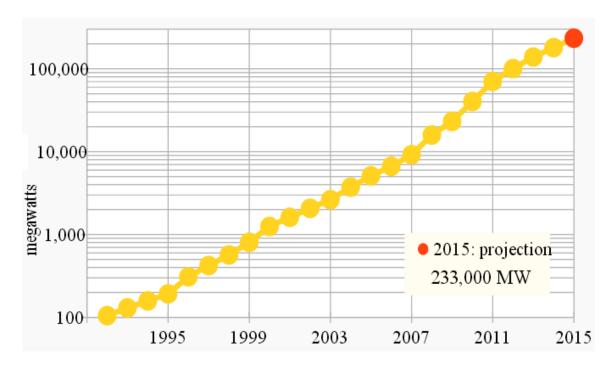

From 2003, global PV productions have increased ten times with annual growth 40-80%. This cumulative capacity will be reached 233 GW in 2015. Their increasing trend and projection is shown in the graph, figure 1.2.

Figure 1.2 Global cumulative PV Capacity in MW since 1990

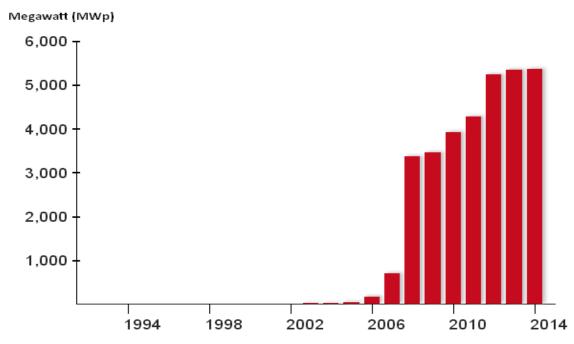

In Spain, coverage of electricity demand from solar energy has experimented in the beginning of 2004 (first decay of twenty-first century), up to 3-5% energy accumulated from solar resources [9]. In 2009-10, the many PV power plants were installed in Spain, the most common PV power plants are Olmedilla Photovoltaic Park (60 MW), Puertollano Photovoltaic Park (47.6 MW), Solar Plant La Magascona and Magasquila (34.5 MW), Arnedo Solar Plant (34 MW), and Dulcinea Solar Plant (31.8 MW). The Spanish situation were very significant in manufacturing worldwide from 90 and thanks to the existence of strong industrial groups, those are leader in manufacturing photovoltaic cells/panels in Spain, emerged as a spin-off of university research groups and in all the cases providing good support in R & D (research and development).

In 2009 due to political restriction on renewable energy, photovoltaic industry collapse in Spain. Module fabrication decreased more than 30%. BP solar in Madrid and some other Photovoltaic's companies from Spain even from Europe moved to Asia, especially in China and India due low fabrication and labor cost. But still some companies have endured without closing their setup and come with better prospects and have plans to expand the module fabrication (Photon January 2010 issue).

Figure 1.3 Photovoltaic solar energy in Spain since 1992, in megawatts (MWp)

As photovoltaic industry is rapidly growing industry in last 2 decade also known as high technology corresponding electronics sector as well as microelectronic and nanotechnology sector.

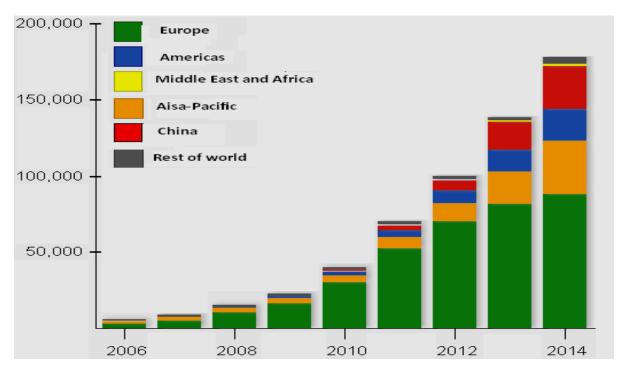

The global growth of photovoltaics (PV) has been fitted by an exponential curve for more than 2 decades. During this period, PV solar progressed from small scale application toward to become main source of electricity. By the end of 2014, global cumulative photovoltaics capacity researched at 178 gigawatts (GW). This is sufficient to supply 1% of overall electricity demand. For 2015, global deployment of being about 55GW is forecasted and installed capacity is projected to be more than double beyond 500GW between now and 2020. In 2050 solar energy is expected to become the world's largest source of electricity with PV solar cell and concentrated solar power. It will be necessary to grow PV capacity up to 4600GW, of which more than half is forecasted to be deployed in China and India. [10]. Regional wise global cumulative capacity is given in the graph figure 1.4.

Figure 1.4 Cumulative Capacity in Megawatts [MWp] Grouped by Region

#### 1.2.2 Summary; Analysis of state of Art

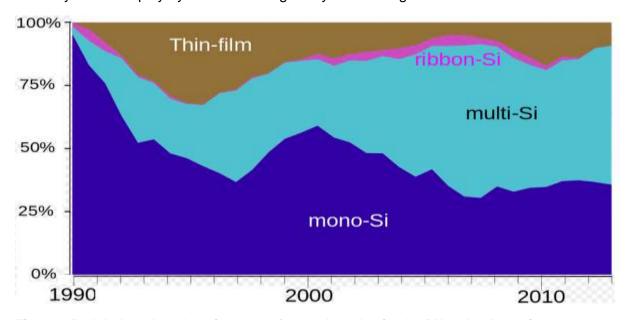

The generations for electricity by using photovoltaic solar module have the highest growth rate which is more than 40% annually over last six years. This growth rate is mainly support by crystalline silicon technology, which is currently contributing more than 90% of the world PV market. More than 90% of solar modules/panels are fabricated by using either monocrystalline or polycrystalline silicon globally. See the figure 1.5 for more detail.

Figure 1.5 Global market-share in terms of annual production by PV technology since 1990

In the recent past, the barrier which exists to massive deployment of photovoltaic solar energy is only its relative high cost as compared to other power/energy generation

technology. It is also true that the calculations which assess the benefits of sustainability of the resources and its environmental impacts, impacts of photovoltaic power resource will be greatly benefits as compared to other power resources.

Now a days these barrier are not well established in distribution of generation, new energetic modules. In our opinion cost reduction does not only depend on the economical scale but also effect of R&D will be significant. Short and medium term technologies support the market that will be an evolution of what will be finding today in line of fabrication/production. While in long terms, we will need of new technologies, perhaps which will be based on better utilization of solar spectrum.

Today more than 90% of photovoltaic solar panels for generation of electricity are based on crystalline silicon wafers which are usually doped with boron and obtaining by casting in the form of monocrystalline and polycrystalline silicon, grown by Czochralski methods. There are many reasons to favor this technology (p-type wafer). On one hand, use of p-type wafers doped with boron, is quite simple to get phosphorus emitters by diffusion which is relatively simple technique, surface is transparent to light, recombination is low enough to give good photocurrent and high open circuit voltage. Moreover phosphorus is more soluble in silicon as compare to silicon oxide. Wafer surface rich in phosphorus could be used for making ohmic contacts even using screen-printing silver paste, in which silver is functional element.

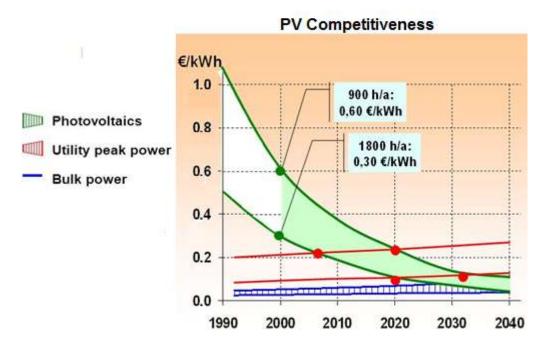

Figure 1.6 Curves of the solar electricity cost and forecasts

Figure 1.7 Electricity generating cost for PV and utility prices

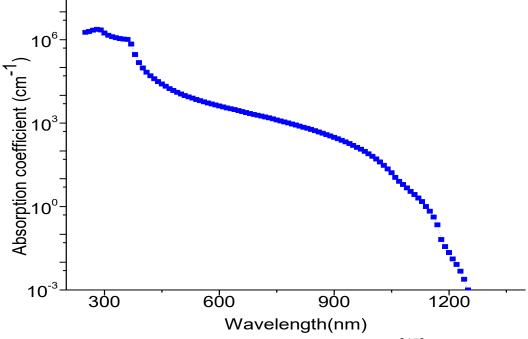

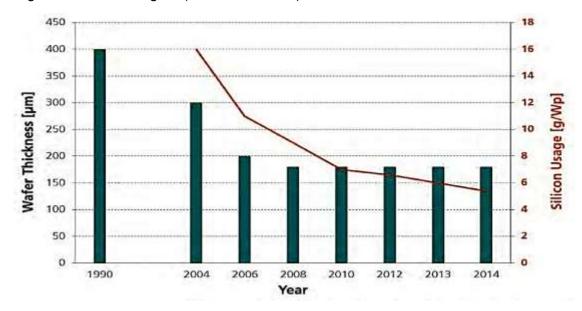

One of most common way to reduce the cost of photovoltaic is to use thin silicon wafers without loss of conversion efficiency of solar cells. Thin silicon wafers create new challenges, in term of their electrical, optical and mechanical characteristics which are different from conventional silicon wafers even handing is more complicated than conventional wafers. First thing which appear in reducing the thickness is back surface of cell, which are little important in conventional cells. It becomes electrically active.

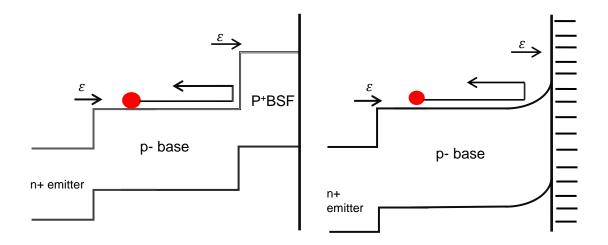

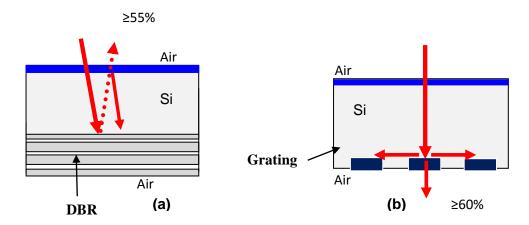

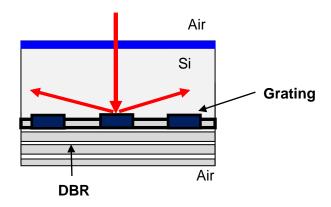

The carriers which are generated by the absorption of light within the cell, electrons which are minority carriers in case of p-type bases, have major possibility to travel till back surface. Instead of being collected by front contacts. If the back surface do not have any kind of electron repelling property like p+BSF, electrons end their journey at this point and recombine at back surface. In addition to this many photons can pass through entire thickness of wafer without being absorbed in semiconductor material. Overcome these 2 problems we have to design the back surface of solar cell which not only reflect the electrons backward but also reflect the photons back toward the base of material to increase the probability of collection/absorption of photons. A structure that combines the existence of a reflector of electrons and photons is BSF layer with aluminum back reflector layer (in case of thin wafers).

The fragility of thin wafers has resulted in significant breaking rates when they are introduced in line of production or when treated at high temperature [11]. On contrary to thick wafers, thin wafers are more flexible behavior and difficult to handle, Due to this reason, thin wafers must be handled in special way in order to avoid breakage and damages. We have found that thin wafers can be bent to a minimum bend radius and exceeded radius may break the wafers. [12]. Fraunhofer ISE Institute also concluded the existence of minimum radius [14].

The industrial fabrications of silicon solar cells which are based on thin wafers require a better understanding of their mechanical properties. Our institution TIM-EHU also

participated and collaborated with other research groups in different research projects (Cesidel Bimude 2007 thin cells, christhin, and Tobaco) were working on resistances, strength and mechanical properties of material, concluded that there is no relationship between the radius of curvature and thickness of wafers. Wafers are broken due to surface cracks which appear during cutting and processing of wafers by wire saw. It may be deeper than 30  $\mu$ m [15].

Measurement and analysis of surface of wafers which are removed by chemical etching support the wafers for greater stresses without breaking and consequently smaller radii. [15]. Due to this reason, it seems that thin wafers, which are obtained by thinning of thick wafers by chemical etching, have very low bending radii and high maximum voltages.

At industrial scale, the efficiency that can be obtained by silicon solar cell is range from 16-19% depending on the process and material used. The first industrial technology have presented higher efficiencies than 15% are LGBC (Laser grooved buried contacts) by BP-solar or PCSC (point contacts solar cells) employed by SunPower with efficiency 20%. [16]. In case of SunPower (solar cell fabricating company), the solar cells fabricated by using silicon grown by FZ (float-zone) technology, in order to ensure the necessary high lifetimes. Sanyo solar, commercializing solar module panels with HIT technology (Heterojunction with Intrinsic Thin-layer) new technology, announces modules with cells of 18.5 % [17].

The objective of this thesis is to achieve (P/Al) AlSi industrial technology with cell efficiencies around 18% and thickness of 150  $\mu$ m. This objective will strongly improve the high efficiency cell fabrication for future. In our opinion there are many technologies which exist in production line, which can be use carefully for mechanical handling of wafers up to 150  $\mu$ m thick. In addition to this, all our knowledge about mechanical behavior of thin wafer, one part of our work strategy is to optimize the amount of aluminum deposited on backside by using electron beam machine and thermal processing parameters such temperature and diffusion time. These paste which are based on composite of boron and aluminum, it will allow using technology aluminum alloy on backside of wafer of 150  $\mu$ m thick [18]. As we know, from experimental results, screen printing paste of silver can produce deformation at front surface of the cell. For proper handling of geometry of front electrical contacts, the composition of the glass-frit of the paste and proper condition of firing (time and temperature) allows partially to compensate the tension/problem caused by the alloy of Al-Si of backside.

The efficiency of solar cell either can be increased by using high quality substrates (FZ-silicon) as it was the case of SunPower or by using low temperature processes and excellent passivation of surface as in case of Sanyo HIT cells. In both cases, high quality of base of material must be assured. However, these technology are expensive and we do not believe that high cost of FZ silicon allow these technologies to be competitive with other technologies. With respect to low temperature process, those involve a large number of variations on conventional process. Process such as HIT, it includes a large number of steps in plasma equipment for deposition of amorphous silicon layers. From there, it is necessary to look exquisitely entire thermal process, in order to avoid amorphous silicon not to crystallize. Crystallization may destroy the passivation properties of cells. It is necessary to synthesize screen printing paste for new metallization at commercial scale availability for low temperature fire 750 °C. In short, it looks a very complex and uncertain competitive process.

The option is selected to implement a process which is based on AlSi, in which phosphorus is supersaturated at front surface and aluminum alloy on back surface. These processes ensure high lifetime of electrons in material and important source of gettering of metallic impurities. This process will be compatible with monocrystalline or polycrystalline silicon wafers, while wafer will be based on monocrystalline Cz industrial wafers.

Increase of efficiency of these solar cells will be based on formation of lightly doped deep phosphorus emitters, which is usually formed by using phosphorus diffusion in saturated conditions. However in case of phosphorus gettering is compromised and high diffusion time is required which severely limit productivity of the process.

There are two technical problems which must be solved for utilization of deep emitters. First is surface passivation for lightly doped deep emitters, passivation will be done by applying SixNy layer in plasma equipment by PECVD. Second is the electrical contact of emitters, which is complex due to specific contact resistance of silver pastes. It dramatically increases with decreasing surface concentration of impurities. For this process which we proposed the use of selective emitters incorporating phosphorus dopant, with this technology we expect to obtain an efficiency of 16.5%.

Selective emitters are already used in some industrial technologies, as SunPower cells and LGBC (Laser grooved buried contact) in case of BP-Solar. Recently two German groups have shown that is possible to form emitters in case of aluminum and phosphorus through laser.

#### 1.3 Description of P/Al technology

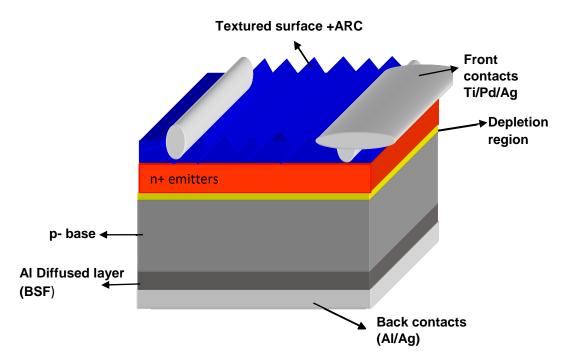

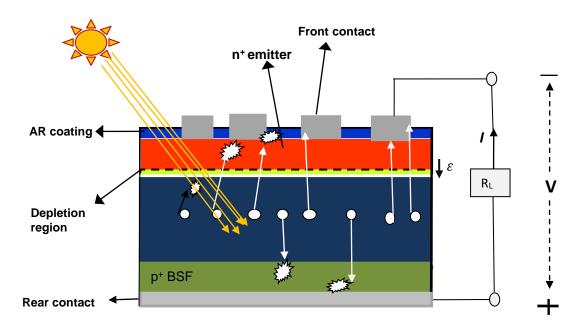

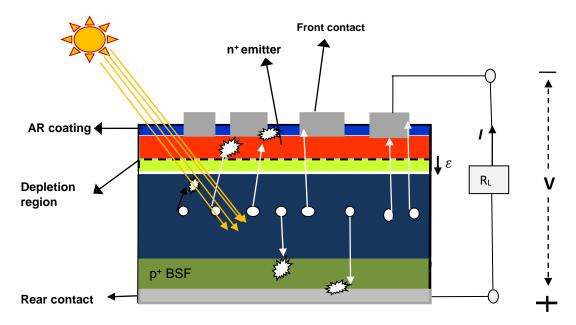

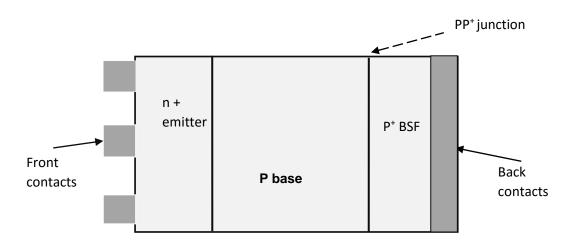

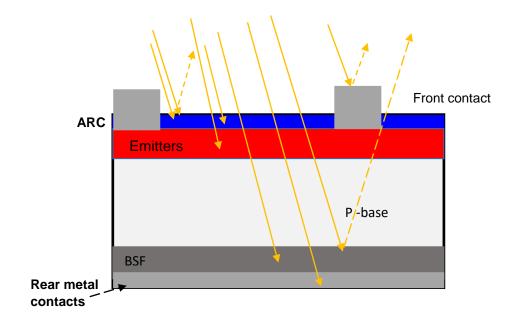

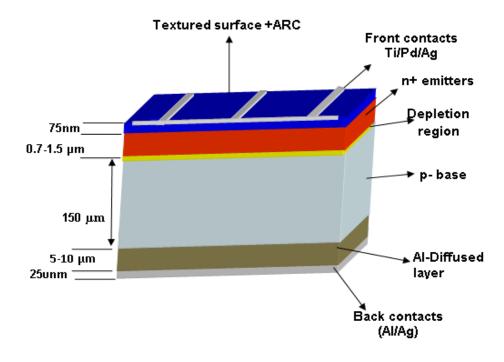

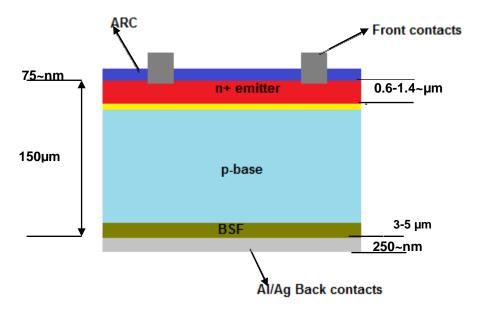

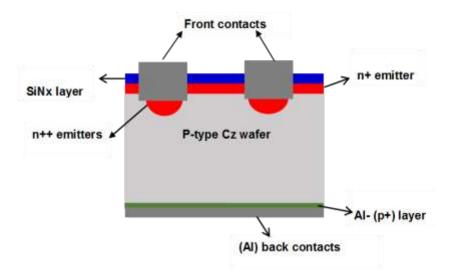

In the mid of 80's, theoretical and experimental studies of A. Cuevas and M. Balbuena have given a conclusion that it is possible to obtain high efficiency with lightly doped deep phosphorus emitters and aluminum back surface field, P/AI (P emitters- AI BSF). They have obtained efficiency around 19% by using high quality FZ (float zone) monocrystalline silicon wafers [6]. In fact when the process was described in mid of 80's, efficiency achieved was remarkable and among the best silicon solar efficiency reported in the world. The structure of P/AI solar cell is shown in figure below.

Figure 1.8 Structure of standard P/Al solar cell

The P/Al structure mentioned above of high efficiency can apply to other materials with simplicity; it can be considered useful tool to evaluate the, solar grade potential of materials for photovoltaic application both for monocrystalline and polycrystalline silicon.

The main features of this fabricating process, which we can call as standard process, is consist of simultaneous diffusion for formation of front phosphorus emitters and back surface region as a highly doped aluminum as back surface field.

#### 1.3.1 Research objective:

In this work, we have focused on the fabrication of P/Al solar cells with high efficiency process around 18% by using Cz wafers (other than FZ wafers). The research objective is divided into the following specific tasks:

#### 1.3.2 Task1: Lightly doped phosphorus emitters

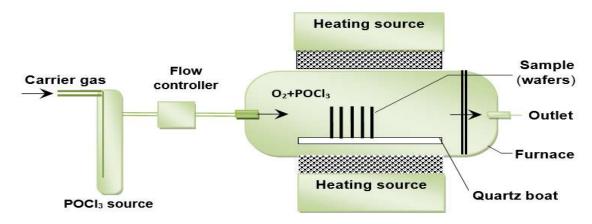

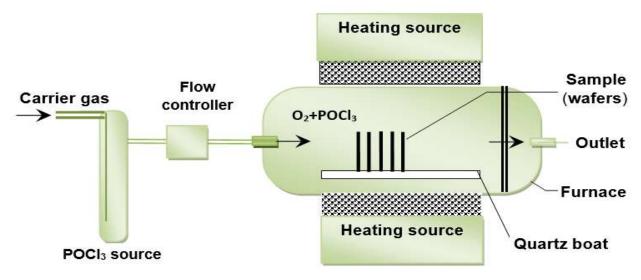

One of objective of this work is get lightly doped homogeneous P emitters with moderate surface concentration. Conventional phosphorus emitters doped by using screen printing technique are in range of 40-60  $\Omega/\Box$  and different characteristic of expected cells are studied by analyzing PCD (Photo conductance decay) and Sun-Voc (irradiance versus open circuit voltage) techniques. For homogeneous emitters, P doping is carried out by diffusion in a quartz tube by passing nitrogen gas through a POCl<sub>3</sub> source understand different temperature and quartz furnace conditions. Addition to this we have evaluated sheet resistance, surface concentration and junction depth. Deep emitters which are around  $100\Omega/\Box$ , provide high efficiency.

#### 1.3.3 Selective phosphorus emitter

Conventional homogeneous emitters are formed over full area of silicon wafer by using POCl<sub>3</sub> as a source of phosphorus at 800-875 °C and nitrogen as a carrier gas in tube furnace under standard conditions. Selective emitters are doped selectively with P either by using a tube furnace or other means such as laser, inkjet are called selective emitters. For selectivity of emitters, these are lightly doped under passivated area, open for illumination and heavily doped under metallic contacts. These emitters allow to be metalized by industrial techniques such as screen printing and ink-jet.

#### 1.3.4 Task2: Surface passivation

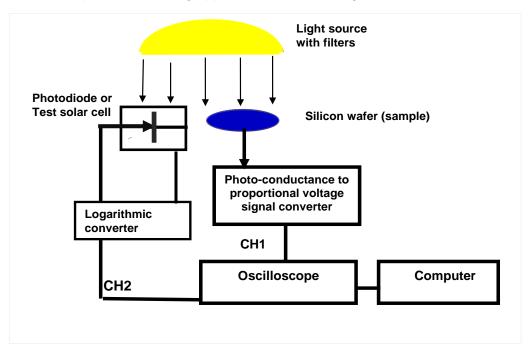

Front surface passivation we focused on silicon nitride and tandem silicon oxide. Silicon nitride not only passivates the surface but also acts as antireflection layer which is important for high efficiency process. While in case of back surface passivation, Aluminum has been deposited on backside of wafer by electron beam machine and disseminated in quartz furnace (diffuse deeper inside silicon). The extraction of impurities or gettering as well as effect of BSF layer (Back surface field) has been assessed through lifetime and sun-Voc measurements.

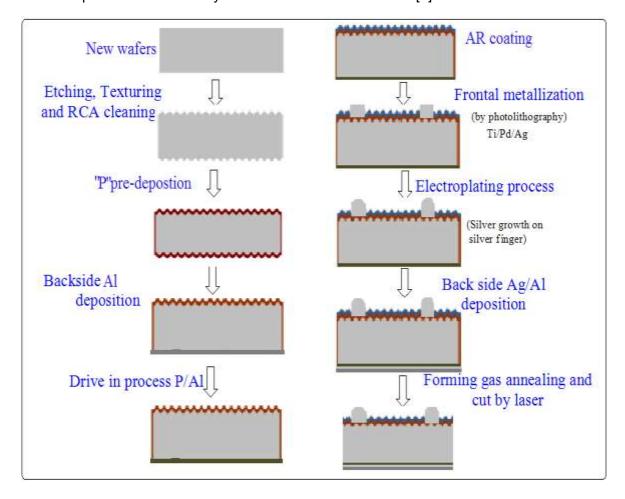

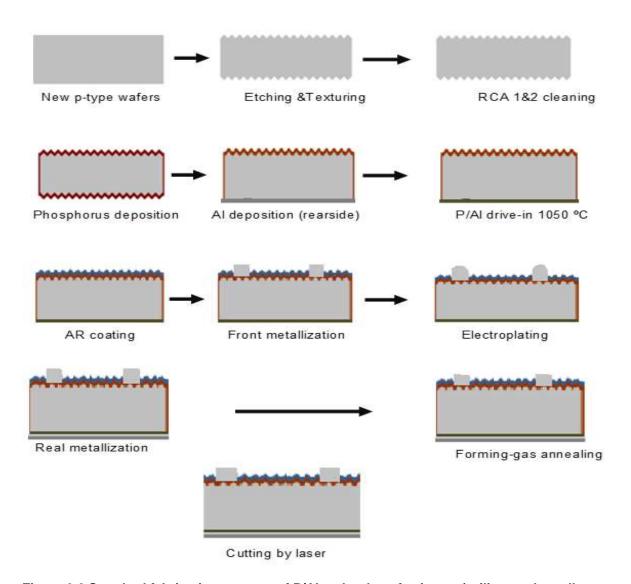

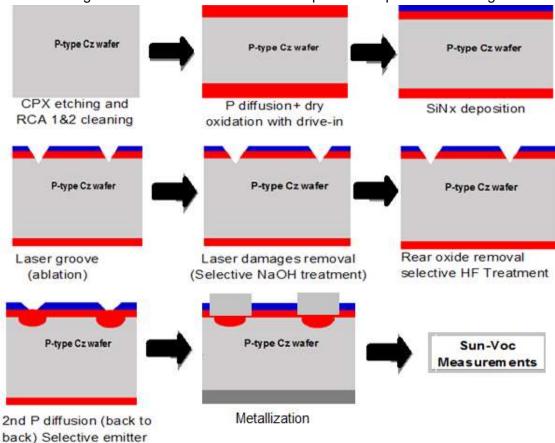

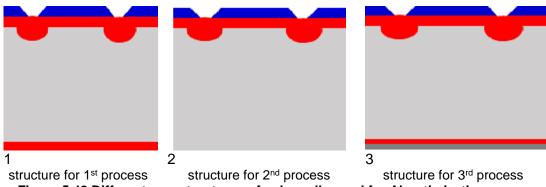

P/Al process for solar cells fabrication is shown in figure 1.9 which also represents the minor tasks with little modifications. Process used in this work is modified as compare to standard process described by A. Cuevas and M. Balbuena. [6]

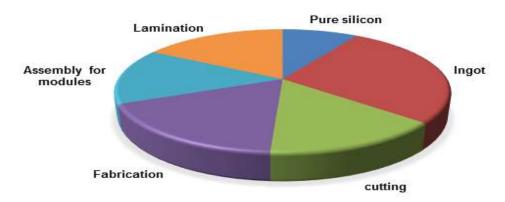

Figure 1.9 Typical silicon solar cell fabrication steps by using P/AI standard process

Lot of work has been done to improve this standard P/Al process and to reduce the fabrication cost by modifying the technological steps. Our main objective is similar, to improve this P/Al standard process for high efficiency and to reduce the cost. In future this standard process will be apply for industrial silicon solar cells fabrication.

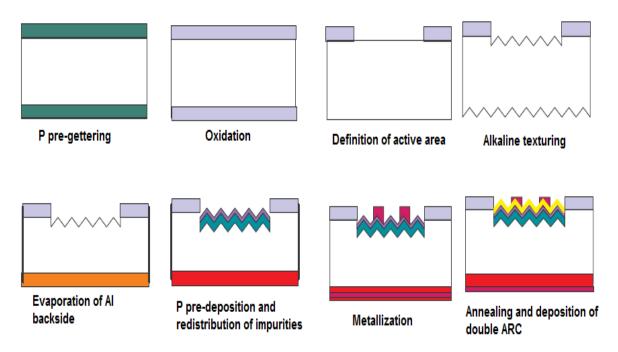

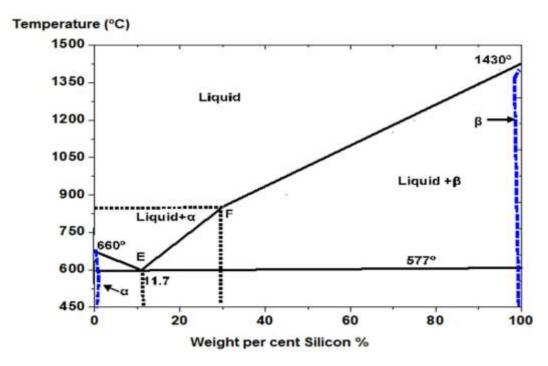

Standard P/Al process was design and developed in Institute of Solar Energy, Polytechnic university of Madrid (IES-UPM). This process was first time investigated by J. Alonso on Float-zone wafers of different resistivity. The results are given in doctoral thesis [19]. Subsequently Rosa Lago performed various process of P/Al on Cz wafers supplied by Bayer. She used Cz p-type wafers with resistivity 1.4  $\Omega$ .cm and 130-170  $\mu$ m in thickness, the best result are given in the table 1.1 [7]. Later A. Mousaousi optimized this process to apply on multicrystalline materials with resistivity 0.5  $\Omega$ .cm. During this investigation, A. Mousaousi made some modification in standard process. In this new process, he had introduced novelty in initial step of extracting the impurities by phosphorus that is called pre-gettering. In addition to this, new process reduced the thermal budget by uniting step P predisposition and P and Al drive in (redistribution) in one step. Detail of process is given below;

- 1. "P" pre-gettering step at 850 °C for 30 minutes, Thus it improves the lifetime of wafers, over all solar cell characteristics will be improved. Etching process removes the diffused area from both sides.

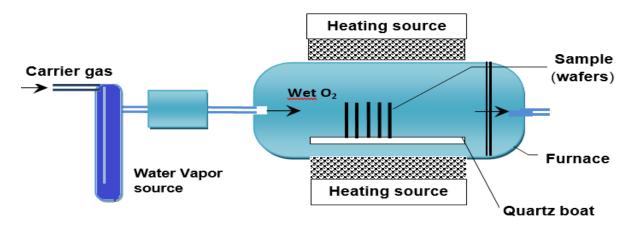

- 2. Thermal oxidation of wafers in both dry and wet conditions at 950 °C for 4 hours.

- 3. Defining the active area on front surface by photolithography and removal of oxides from window, where solar cell to be placed and whole back surface.

- 4. Alkaline texturing of surface.

- 5. Evaporation of Aluminum 1µm thick on backside of wafer.

- 6. For P pre-deposition and redistribution of impurities, optimum temperature was chosen, was 900 °C for 12 hours. During this step, emitters with depth junction 0.5 µm and surface concentration of 5x10<sup>19</sup>/cm³ was achieved with passivated surface.

- 7. Metallization of front contacts was carried by electron beam machine by using photolithographic technique. Metallization of back contacts was carried out by evaporation by EBM.

- 8. Forming gas annealing at 450 °C for 20 minutes (90% nitrogen and 10% hydrogen).

- 9. Finally deposition of double antireflection layer (ZnS + MgF2).

Figure 1.10 Solar cell fabrication processes at moderate temperature by simultaneous diffusion of P and AI [12]

Table1.1 shows typical results of standard P/AI process obtained during solar cell fabrication by using Float zone substrate (high quality wafers), Cz substrate (low quality wafers) and multicrystalline substrate.

Table 1.1

| Type of wafers              | Voc     | Jsc                  | FF    | Efficiency | References |

|-----------------------------|---------|----------------------|-------|------------|------------|

| (Resistivity in Ω.cm)       | (mV)    | (A/cm <sup>2</sup> ) | (%)   | (%)        |            |

| Monocrystaline FZ (0.3)     | 645-650 | 35                   | 75-83 | 17.5-19    | (6)        |

| Monocrystaline FZ (0.3)     | 645-650 | 35                   | 81-83 | 18.5       | (19)       |

| Monocrystaline FZ (1)       | 628-632 | 37-38                | 81    | 18.5-19.5  | (19)       |

| Monocrystaline FZ (20)      | 612-618 | 38-39.5              | 79-81 | 18.5-19    | (19)       |

| Monocrystaline CZ (1.4)     | 603     | 33.5                 | 79    | 15.9       | (7)        |

| Monocrystaline CZ (0.5-1.5) | 602     | 35.4                 | 82    | 17.5       | (7)        |

| Monocrystaline CZ (0.5-1.5) | 601     | 36                   | 83    | 17.8       | (7)        |

| multicrystalline (0.5)      | 635     | 34.1                 | 79.7  | 17.3       | (20)       |

| Multicrystalline<br>(1.5)   | 611     | 33.5                 | 74    | 15.3       | (21)       |

In A. Mousaousi P/AI fabrication process, high lifetime was measured along with high efficiency on multcrystalline wafers. Although this process has advantage of high efficiency with high lifetime but this process has disadvantage of long duration of P pre-deposition step and redistribution of impurities (step 6 as mentioned above). Its high thermal load made this process unsuitable for other substrate. In addition to this process has low reproducibility [20].

| Initial lifetime | After P pre-gettering | Final lifetime |

|------------------|-----------------------|----------------|

| (µs)             | (µs)                  | (µs)           |

|                  |                       |                |

| 30               | 100                   | 105            |

|                  |                       |                |

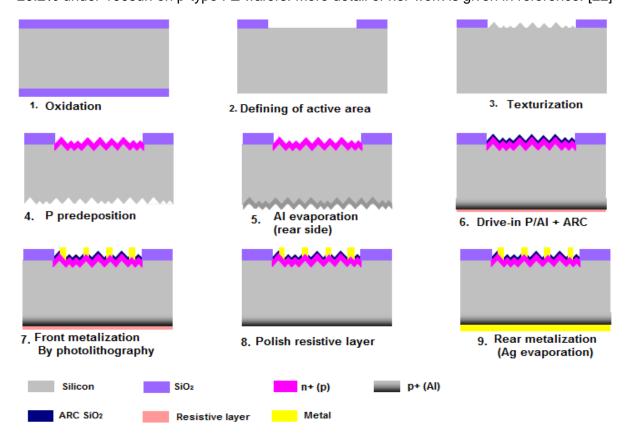

After A. Mousaousi, S. P. Alcántara investigated fabrication of multicrystalline silicon solar cells by using P/AI process with high resistivity. In this process the innovation was simultaneous extraction of impurities by phosphorus and aluminum which is called cogettering process. But due to high temperature, lifetime was affected, S.P. Alcántara more focused on improvement of lifetime by using passivation technique. The best of results of his research are given in table 1.1 [21]. Later M. C. Delgado was working on fabrication of silicon solar cell under concentrated light by using P/AI technology, with minor modification in concept of cost reduction and industrialization at UPM and UPV/EHU. Flow sheet of fabrication process is shown in figure 1.11. During her investigation and fabricating process of solar cells, she has obtained average efficiency around 18.5% and maximum efficiency 20.2% under 100sun on p-type FZ wafers. More detail of her work is given in reference. [22]

Figure 1.11 Fabrication process of solar cell at UPM-PPV

#### 1.4 References:

- [1] T. Bruton, G. Luthardt, and K. D. Rasch, "A study of The Manufacturing at 500 MWp p.a. of Crystalline Silicon Photovotaic Modules", Proceedings of the 14th European Photovoltaic Solar Energy Conference, 11-6, 1997.

- [2] Wikipedia.org/wiki/Solar\_cell

- [3] D. M. Chapin, C. S. Fuller, G. L. Pearson, J. Appl. Phys. 25, 676, 1954.

- [4] M. D. Archer, R. Hill, "Clean Electricity from Photovoltaics", Series on Photoconversion of Solar Energy, Vol. 1, Imperial College Press, London 2001.

- [5] A. Goetzberger, C. Hebling, Sol. Energy Mater. Sol. Cells 1, 62, 2000.

- [6] A. Cuevas y M. Balbuena, "Thick emitter silicon solar cells", Proc. 20th IEEE Photovoltaic Specialists Conference, Las Vegas pp. 429-434, 1988.

- [7] R. Lago-Aurrekoetxea, "Recombinación superficial y de volumen en células solares con tecnología fósforo-aluminio sobre silicio", Tesis Doctoral, Instituto de Energía Solar, Universidad Politécnica de Madrid 2002.

- [8] R. Lago-Aurrekoetxea, C. del Cañizo, I. Tobías, and A. Luque, "Measurement of bulk and rear recombination components and application to solar cells with an Al back layer", Solid State Electronics 49 pp. 49-55, 2005.

- [9] Wikipedia.org/wiki/Solar power in Spain

- [10] "Technology Roadmap: Photovoltaic Solar Energy". IEA. Archived from the Original on 7 October 2014. (www.iea.org).

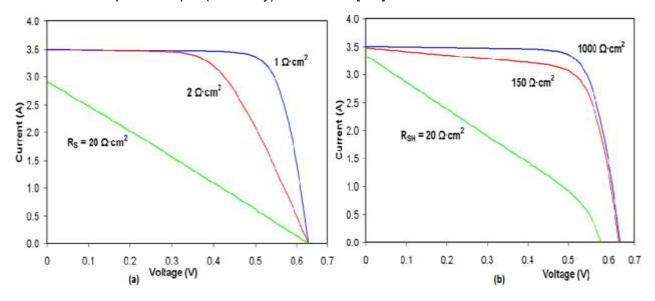

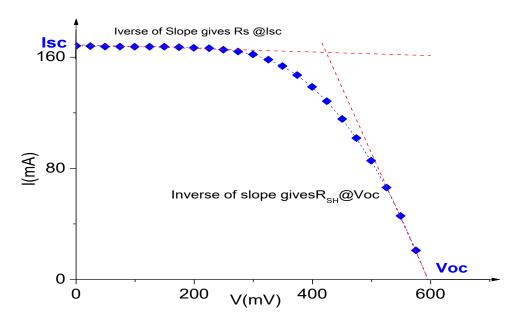

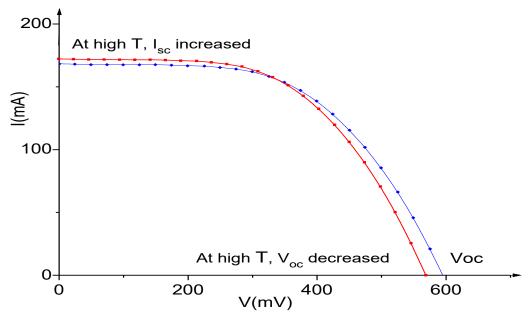

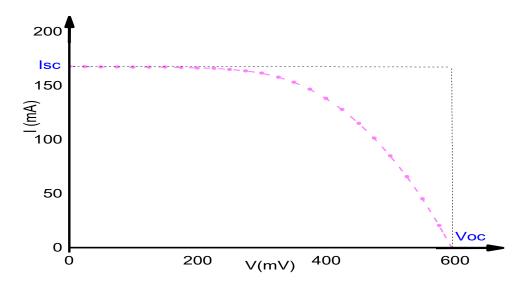

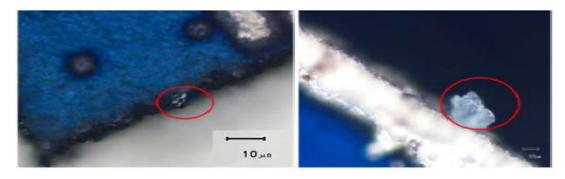

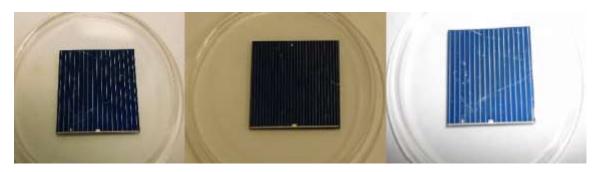

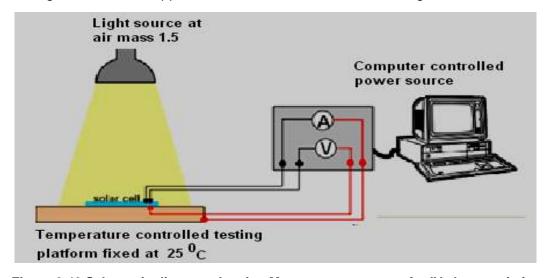

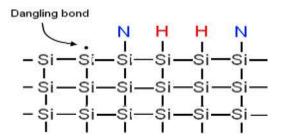

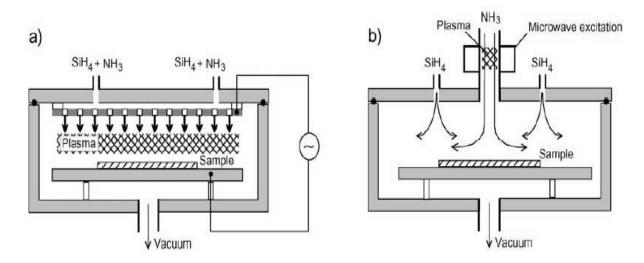

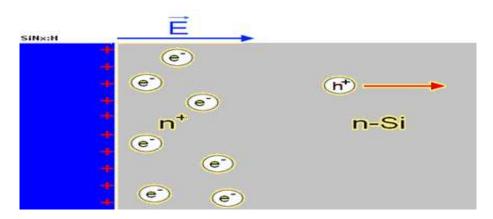

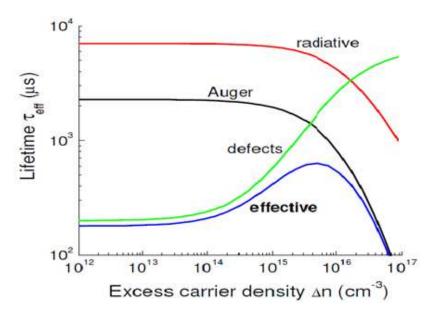

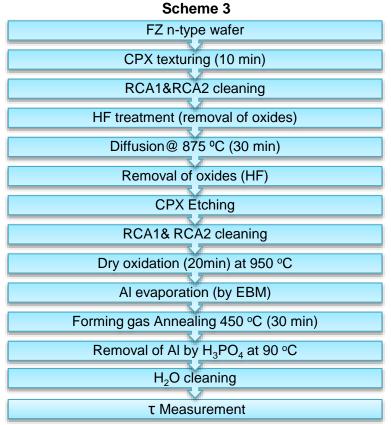

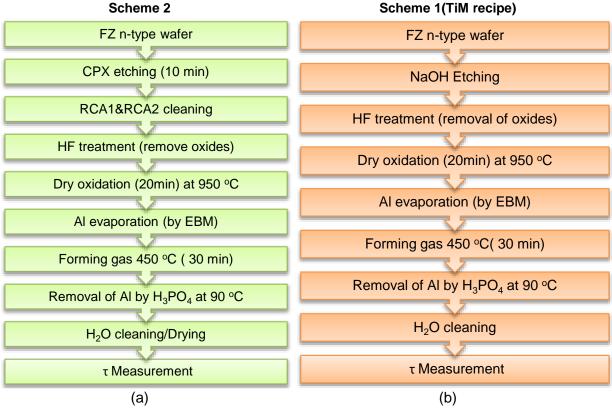

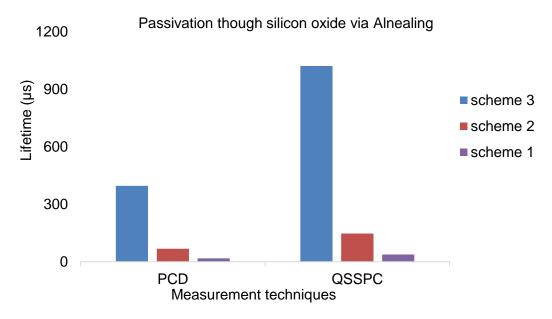

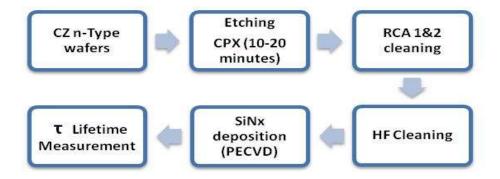

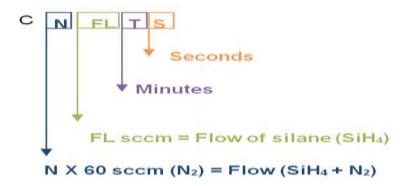

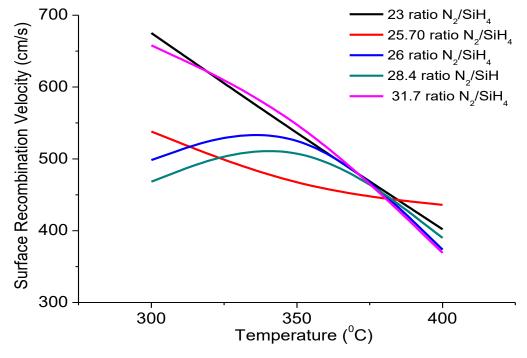

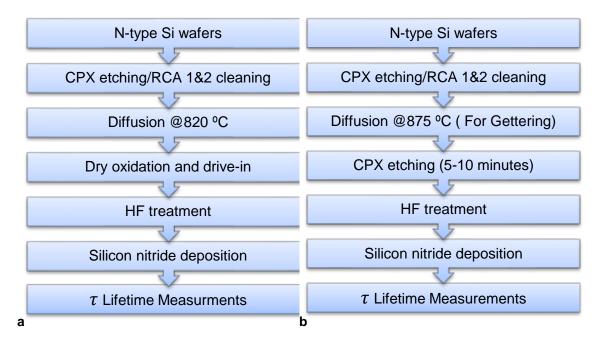

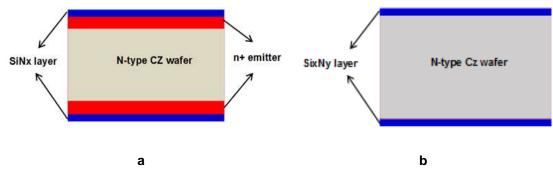

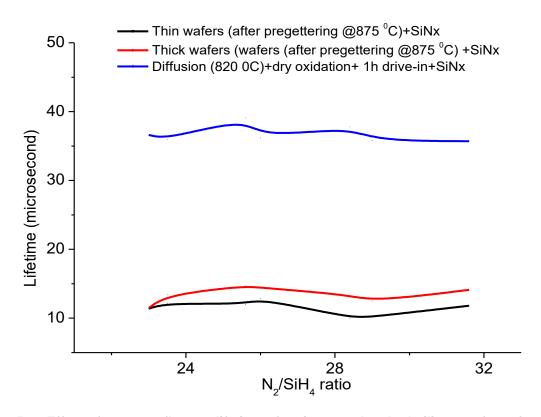

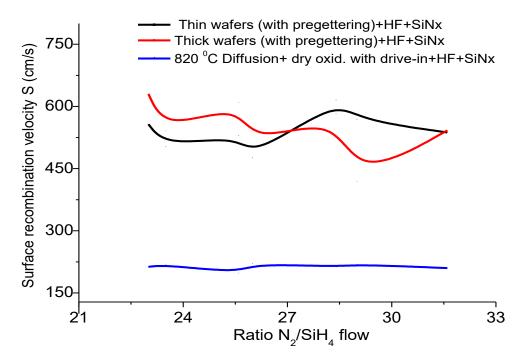

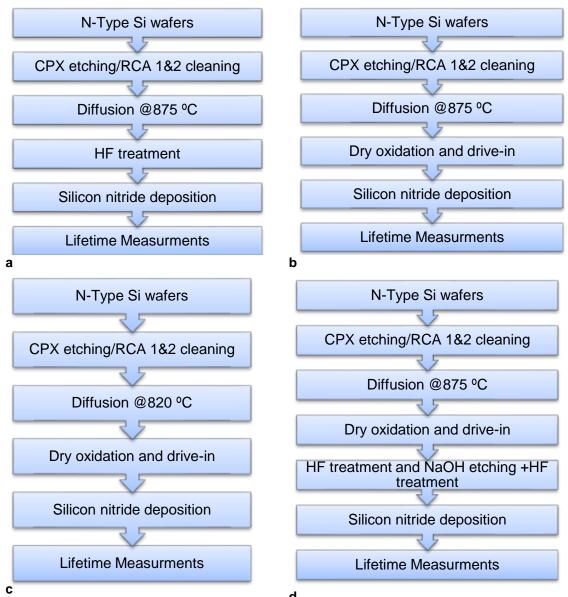

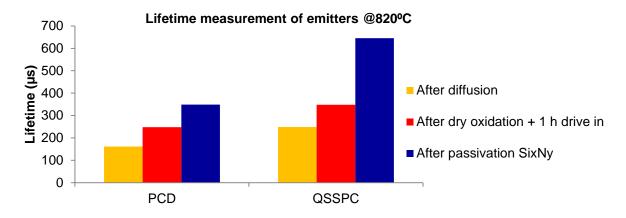

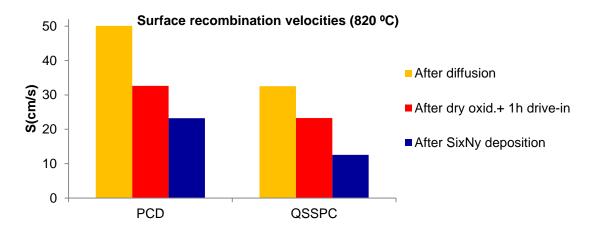

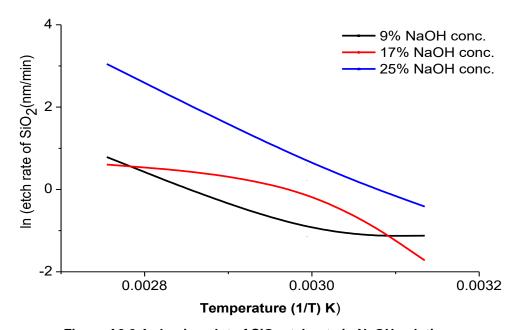

- [11] K. A. Münzer, K.T. Holdermann, R.E. Schlosser and S.Sterk, "Thin Monocrystalline Silicon Solar Cells". IEEE Transactions on Electron Devices, Vol. 46, No. 10. October 1999.