# **MASTER`S DEGREE IN**

# **INTEGRATION OF RENEWABLE ENERGIES INTO THE**

# **ELECTRICAL POWER SYSTEM**

# **MASTER'S THESIS**

# MODELLING OF RESISTIVE TYPE SUPERCONDUCTING FAULT CURRENT LIMITER FOR MULTI-TERMINAL HVDC SYSTEMS

Student Supervisor Marene Larruskain Department Curso académico

García Plasencia, Guillermo Agurtzane Etxegarai, Dunixe

*Electrical Engineering Deparment* 2020/2021

Bilbao, 10 of September of 2021

# INDEX

| 1. INTRODUCTION                                    | 1 |

|----------------------------------------------------|---|

| 1.1 BACKGROUNG                                     | 1 |

| 1.1.1 Fault Current Limiters                       | 2 |

| 1.1.2 HVDC development                             | 3 |

| 1.2 OBJECTIVES OF MASTER'S THESIS                  | 5 |

| 2. HVDC SYSTEMS                                    | 5 |

| 2.1 Converter technology                           | 7 |

| 2.1.1 Line Commutated Converters                   | 7 |

| 2.1.2 Voltage Source Converter                     | 8 |

| 2.2 Configurations and introduction to HVDC grids1 | 0 |

| 2.2.1 System configuration1                        | 1 |

| 2.2.2 HVDC grids1                                  | 2 |

| 2.3 HVDC Faults                                    | 5 |

| 2.4 Direct current Circuit Breakers1               | 9 |

| 2.4.1 Mechanical DC circuit breakers2              | 0 |

| 2.4.2 Solid State DC circuit breakers2             | 1 |

| 2.4.3 Hybrid technology DC circuit breakers2       | 2 |

| 2.4.4 Comparison2                                  | 2 |

| 2.5 HVDC grids and protections2                    | 3 |

| 2.5.1 Real example HVDC grids and protections2     | 3 |

| 2.5.2 Proposed protection scheme                   | 6 |

| 3. STATE OF THE ART OF R-SFCL                      | 8 |

| 3.1 Superconducting fault current limiters         | 9 |

| 3.1.1 Principle of operation                       | 0 |

| 3.1.2 Types of SFCL                                | 2 |

| 3.1.3 Design Considerations                        | 5 |

| 3.1.4 Implementation of Real R-SFCL                | 9 |

| 3.2 Modelling of the R-SFCL                        | 4 |

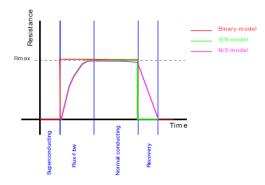

| 3.2.1 Simplified Models4                           | 5 |

| 3.2.2 Magneto-Thermal Models4                      | 5 |

| 3.2.3 Finite Element Modelling                     | 2 |

| 3.2.4 Hardware in the Loop5                        | 5 |

| 4. R-SFCL MODELS SIMULATION                        | 5 |

| 4  | 4.1 Model analysis                     | . 57 |

|----|----------------------------------------|------|

|    | 4.1.1 Step model                       | . 57 |

|    | 4.1.2 Exponential Model                | . 58 |

|    | 4.1.3 R-Q model                        | . 59 |

|    | 4.1.3 Magneto thermal model            | . 61 |

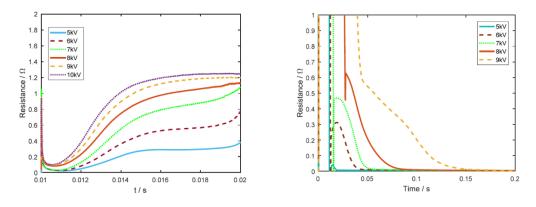

| 4  | 4.2 Model comparison                   | . 62 |

| 5. | MULTITERMINAL HVDC SYSTEM SIMULATION   | . 65 |

| 5  | 5.1 MTDC Fault Phenomena               | . 67 |

|    | 5.1.1 Pole to pole permanent fault     | . 67 |

|    | 5.1.2 Pole to ground permanent fault   | . 68 |

| 5  | 5.2 MTDC System Response With R-SFCL   | . 69 |

|    | 5.2.1 Pole to pole fault with R-SFCL   | . 70 |

|    | 5.2.2 Pole to ground fault with R-SFCL | . 72 |

| 6. | CONCLUSIONS                            | . 74 |

| 7. | FUTURE WORKS                           | . 75 |

# **INDEX OF FIGURES**

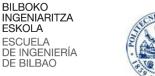

| Figure 1 FCL Types and number of installed devices in real power systems [2]       | 3    |

|------------------------------------------------------------------------------------|------|

| Figure 2 Technical comparison between FCL technologies                             | 3    |

| Figure 3 HVAC vs HVDC cost comparison: (a) economical breakpoint (b) Cost and ROW  |      |

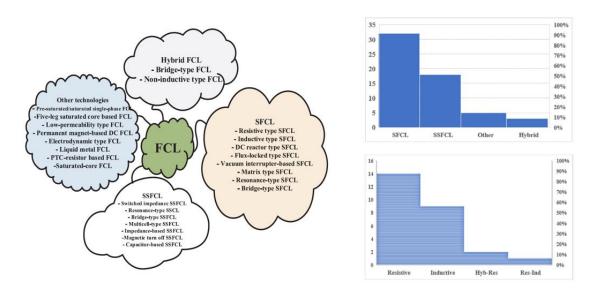

| estimation for 6000MW transmission line of 2000km [6]                              | 4    |

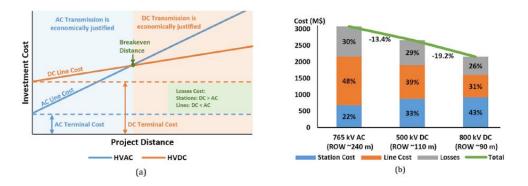

| Figure 4 Evolution of cumulative HVDC capacity                                     | 5    |

| Figure 5 Schematic view of LCC-HVDC system                                         | 7    |

| Figure 6 Main components of the VSC-HVDC system                                    | 8    |

| Figure 7 Conventional 3-Level neutral point clamped converter [13]                 | 9    |

| Figure 8 Most used SM topologies: Full-Bridge (Right), Half-Bridge (Left)          | 9    |

| Figure 9 Schematic of MMC                                                          | . 10 |

| Figure 10 Asymmetrical monopolar configuration                                     | . 11 |

| Figure 11 Grounding options                                                        | . 11 |

| Figure 12 Symmetrical monopolar configuration                                      | . 12 |

| Figure 13 Bipolar configuration                                                    | . 12 |

| Figure 14 Radial topologies; String composition (up), star composition (down)      | . 13 |

| Figure 15 Meshed topologies                                                        | . 13 |

| Figure 16 Possible HVDC grids                                                      | . 14 |

| Figure 17 Four terminal HVDC meshed real grid [16]                                 | . 14 |

| Figure 18 DC Fault types                                                           | . 16 |

| Figure 19 Fault in HVDC grid                                                       | . 16 |

| Figure 20 Events during DC fault                                                   | . 17 |

| Figure 21 Behaviour of the VSC during DC faults                                    | . 18 |

| Figure 22 Comparison of point-to-point system grid (left) and real MTDC (right)    | . 20 |

| Figure 23 Passive resonant mechanical CB                                           | . 21 |

| Figure 24 Active resonant mechanical CB                                            | . 21 |

| Figure 25 Solid-State CB                                                           | . 21 |

| Figure 26 First topology (left) and second topology (right) hybrid circuit breaker | . 22 |

| Figure 27 Diagram of Zhoushan archipelago five-terminal HVDC transmission grid     | . 23 |

| Figure 28 a) Topology b) prototype of the hybrid circuit breaker                   | . 24 |

| Figure 29 Diagram of Nan'ao three terminal HVDC grid                               | . 24 |

| Figure 30 a) Topology b) prototype of the M-DCCB                                   | . 25 |

| Figure 31 Diagram of four terminal grid of Zhangbei                                | . 25 |

| Figure 32 a) Topology b) Prototype of H-DCCB                                       | . 26 |

| Figure 33 Fault current evolution in different scenarios                           | . 27 |

| Figure 34 Currents for all scenarios                                               |      |

| Figure 35 Superconducting M-DCCB with CLR                                          | . 28 |

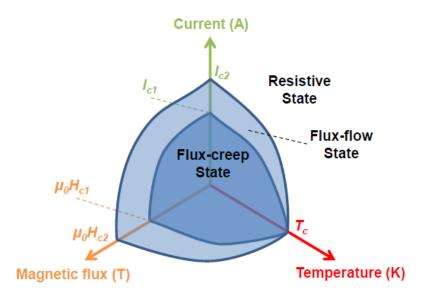

| Figure 36 Conditions needed for superconductivity                                  | . 31 |

| Figure 37 E-J characteristic of HTS materials                                      | . 31 |

| Figure 38 Resistance during quenching process for REBCO                            |      |

| Figure 39 Inductive saturated iron-core [26]                                       |      |

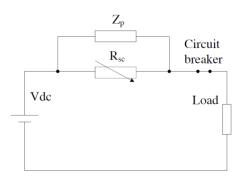

| Figure 40 Electric circuit of a resistive SFCL with parallel impedance             | . 34 |

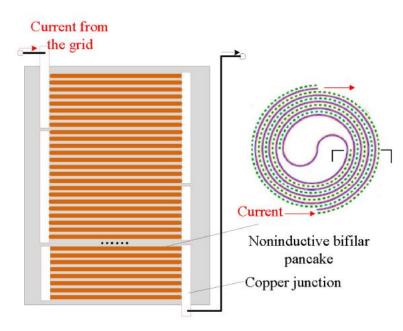

| Figure 41 Configuration of R-SFCL based on non-inductive bifilar pancakes          |      |

| Figure 42 Commercial options of R-SFCL for AC applications                         |      |

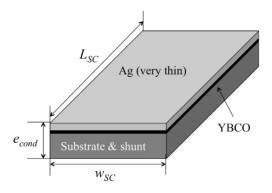

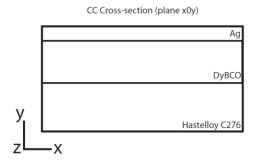

| Figure 43 Simplified cross section of the YBCO coated conductor                    |      |

| Figure 44 Critical current asymmetries of R-SFCL                                   |      |

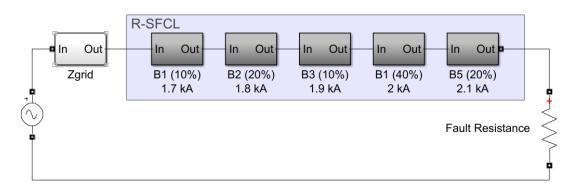

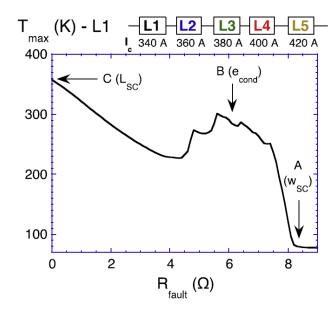

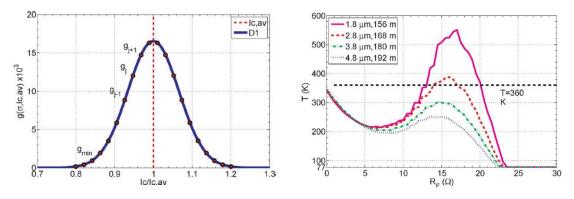

| Figure 45 Maximum temperature Vs Fault resistance (fault current level)            |      |

|                                                                                    |      |

| Figure 46 Commercial superconducting tape from SuperPower                                  | . 40  |

|--------------------------------------------------------------------------------------------|-------|

| Figure 47 Specifications of superconducting tape                                           | . 40  |

| Figure 48 Schematic of the device                                                          | .41   |

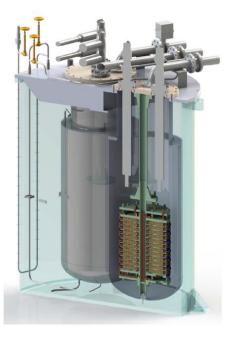

| Figure 49 3D Model of ECCOFLOW                                                             | .41   |

| Figure 50 Distribution of Ic along a conductor with average Ic = 380A (left) and maximum   |       |

| temperature Vs fault resistance (right)                                                    | .41   |

| Figure 51 Complete ECCOFLOW system                                                         | . 42  |

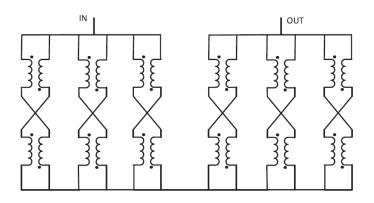

| Figure 52 Coil connection of the R-SFCL                                                    | . 42  |

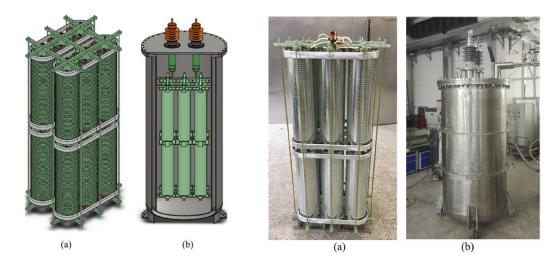

| Figure 53 Structure of R-SFCL (a) and assembly (b)                                         | . 43  |

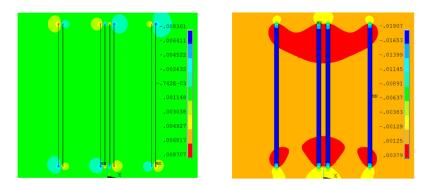

| Figure 54 Magnetic field distribution of R-SFCL; radial component (a), axial component (b) |       |

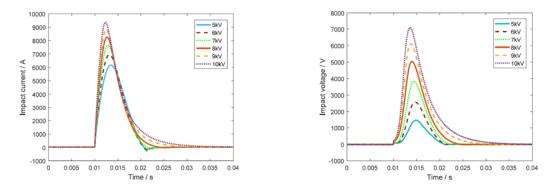

| Figure 55 Current and voltage across the R-SFCL                                            |       |

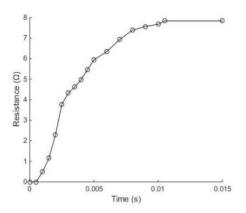

| Figure 56 Evolution of resistance value of R-SFCL                                          | . 44  |

| Figure 57 Evolution of resistance for different models                                     |       |

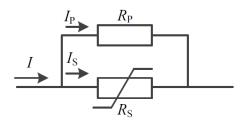

| Figure 58 R-SCFL equivalent circuit                                                        |       |

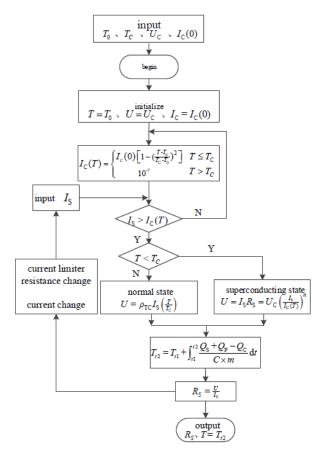

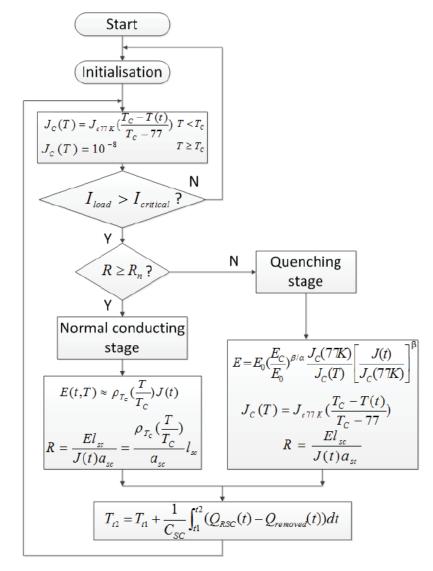

| Figure 59 Flowchart of simulation model                                                    |       |

| Figure 60 1st Approach model resistance evolution                                          |       |

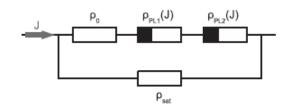

| Figure 61 Representation of R-SFCL as sum of resistances                                   |       |

| Figure 62 3rd Approach model flowchart                                                     |       |

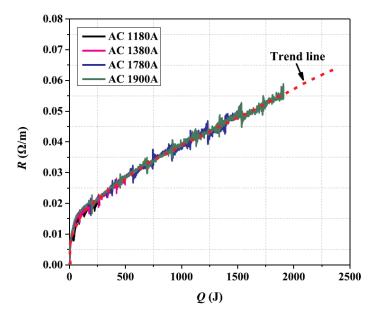

| Figure 63 First R-Q curve for different currents                                           |       |

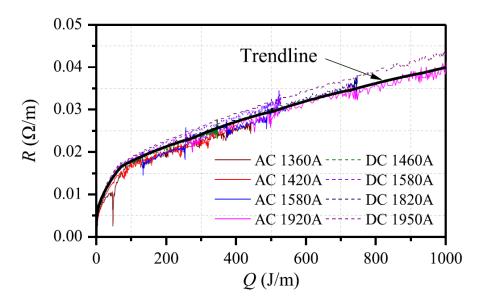

| Figure 64 Second R-Q curve for different currents                                          |       |

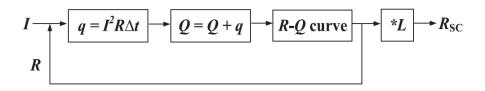

| Figure 65 Resistance calculation method with R-Q curve                                     |       |

| Figure 66 2D geometry of the commercial tape                                               |       |

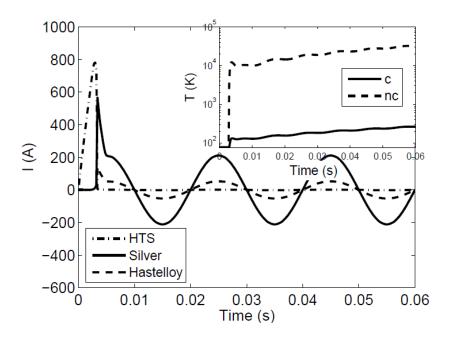

| Figure 67 Current distribution through parallel paths (C shunted - NC not shunted)         |       |

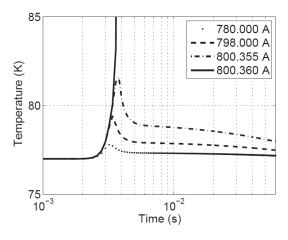

| Figure 68 Thermal stability analysis                                                       |       |

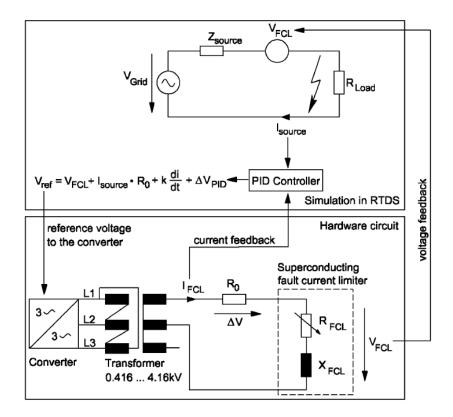

| Figure 69 Conceptual PHIL setup [44]                                                       |       |

| Figure 70 Basic TestBed                                                                    |       |

| Figure 71 M-DCCB with active injection                                                     |       |

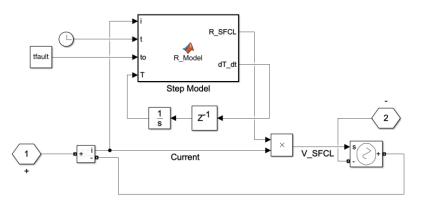

| Figure 72 Step model implementation                                                        |       |

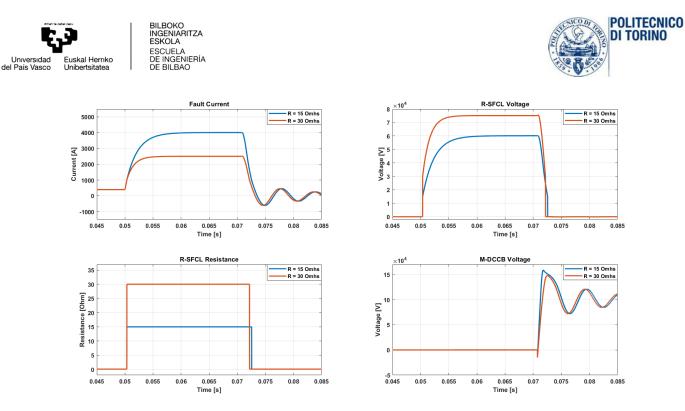

| Figure 73 Step model analysis for different resistive values                               |       |

| Figure 74 Exponential model analysis for different time constants and critical currents    |       |

| Figure 75 R-Q Model implementation                                                         |       |

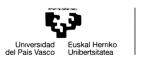

| Figure 76 RQ model analysis for different length and critical current                      |       |

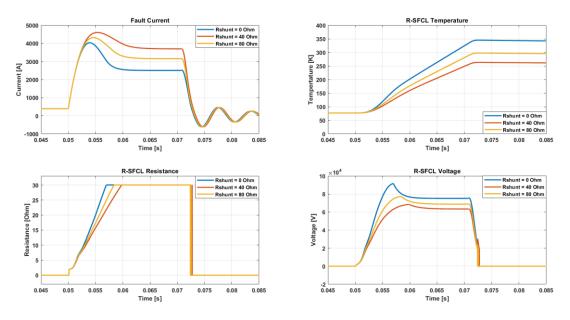

| Figure 77 Fault resistance swept                                                           |       |

| Figure 78 Shunt resistance analysis                                                        |       |

| Figure 79 Magneto Thermal model analysis for different lengths and critical currents       |       |

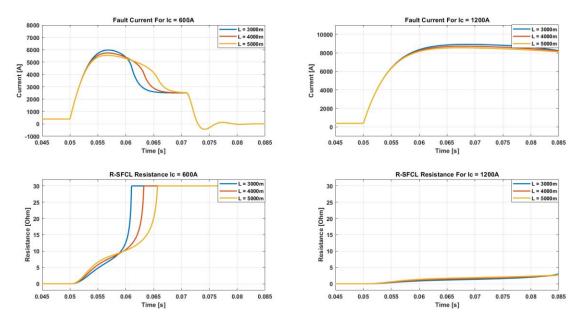

| Figure 80 Fault resistance swept for Ic = 300A                                             |       |

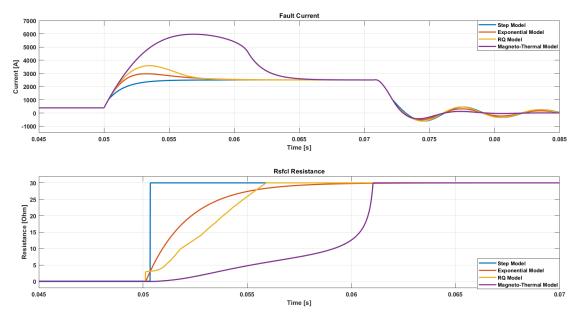

| Figure 81 Superconducting fault current limiter model comparison                           |       |

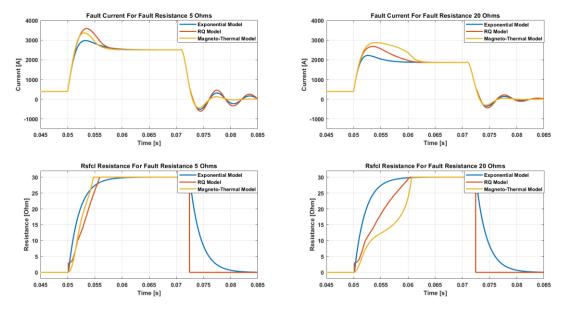

| Figure 82 Model comparison for different fault resistances (Ic@MagnetoThermal = 300A)      |       |

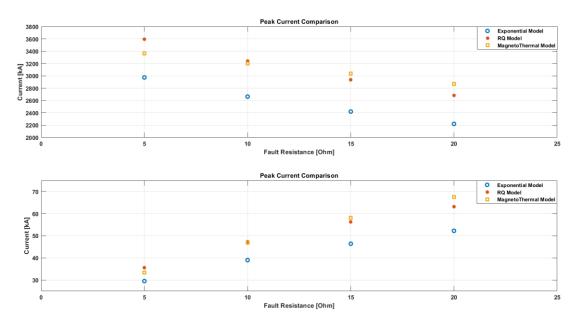

| Figure 83 Peak current and limiting factor for different fault resistances                 |       |

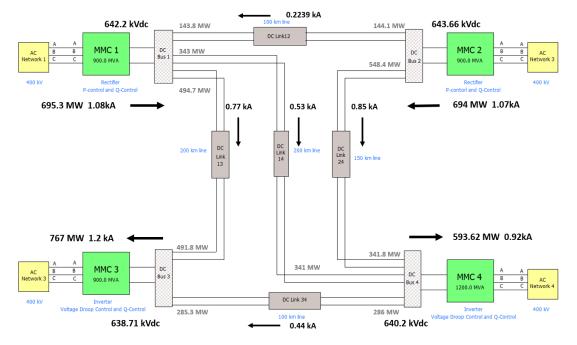

| Figure 84 MTDC test system                                                                 |       |

| Figure 85 System variable illustration                                                     |       |

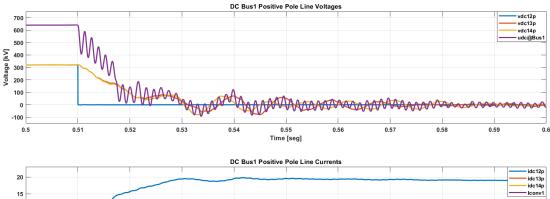

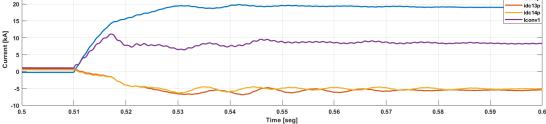

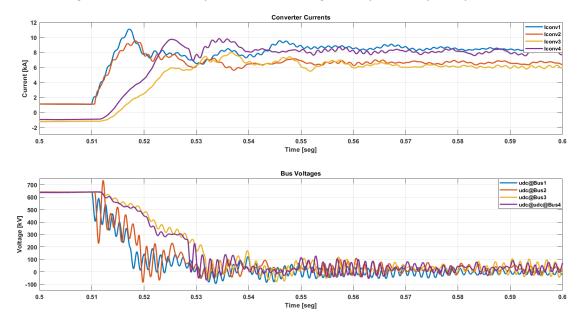

| Figure 86 DC Bus 1 Positive pole currents and voltages when permanent pole to pole occurs  |       |

| Figure 87 Converter currents and BUS voltages when permanent pole to pole occurs           |       |

| Figure 88 DC Bus 1 Positive pole currents and voltages when permanent pole to pole occurs  |       |

| rigure 88 DC Bus 1 Positive pole currents and voltages when permanent pole to ground occ   |       |

| Figure 89 Converter currents and BUS voltages when permanent pole to ground occurs         |       |

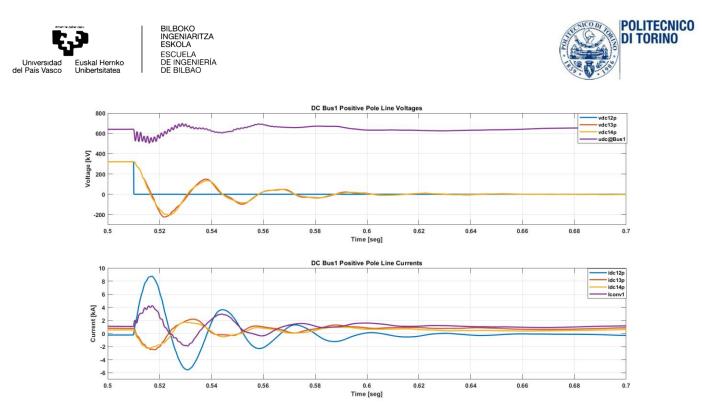

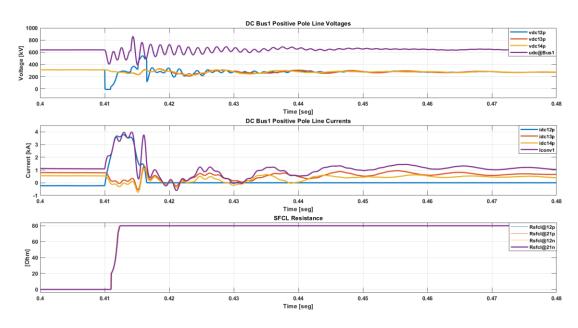

| Figure 90 Positive pole currents and voltages with R-SFCL for pole to pole fault           |       |

| Figure 90 Positive pole currents and voltages with R-SFCL for pole to pole fault           |       |

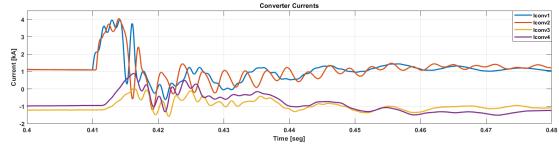

| ingure of converter currents and bus voltages with K-SFCL for pole to pole fault           | . / 1 |

| Figure 92 Peak current reduction per converter for pole to pole fault                       | 71  |

|---------------------------------------------------------------------------------------------|-----|

| Figure 93 Current comparison for pole to pole fault                                         | .72 |

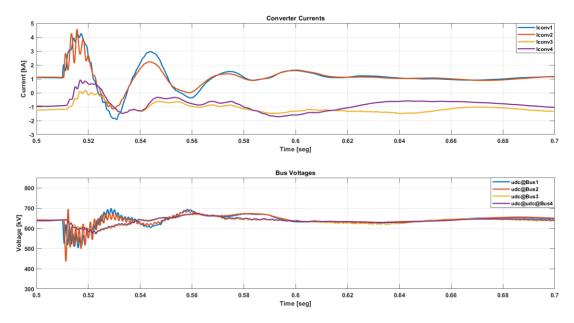

| Figure 94 DC Bus 1 Positive pole currents and voltages with R-SFCL for pole to ground fault | 72  |

| Figure 95 Converter currents and BUS voltages with R-SFCL for pole to ground fault          | 73  |

| Figure 96 Current comparison for pole to ground fault                                       | 73  |

# **INDEX OF TABLES**

| Table 1 HVDC projects evolution                                                      |    |

|--------------------------------------------------------------------------------------|----|

| Table 2 Comparison between LCC and VSC technology                                    | 7  |

| Table 3 Comparison between two-level and multilevel converters fod HVDC applications | 10 |

| Table 4 MTHV projects in China                                                       | 11 |

| Table 5 MTDC grid parameters                                                         | 15 |

| Table 6 Comparison between DCCB tehcnologies                                         | 22 |

| Table 7 Price comparison of copper with superconducting materials                    | 30 |

| Table 8 Latest projects of SCFL up to 2016 [28]                                      | 30 |

| Table 9 Design expression summary                                                    |    |

| Table 10 Key specification values                                                    | 43 |

| Table 11 Parameters of 2 <sup>nd</sup> approach model                                | 48 |

| Table 12 Maxwell Equations                                                           | 53 |

| Table 13 Variable values of TestBed                                                  | 56 |

| Table 14 Parameters of the M-DCCB                                                    | 57 |

| Table 15 Step model settings                                                         | 57 |

| Table 16 Exponential model settings                                                  | 58 |

| Table 17 RQ model settings                                                           | 60 |

| Table 18 Magneto Thermal model settings                                              | 61 |

| Table 19 Model settings for comparison                                               | 63 |

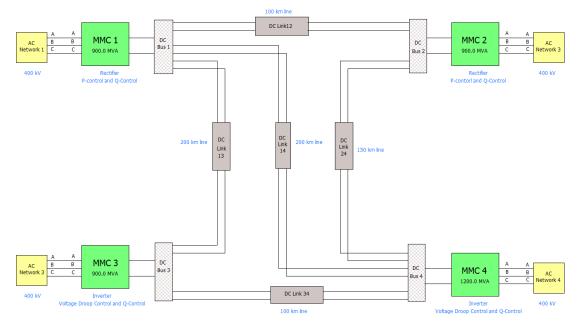

| Table 20 MTDC system parameters                                                      | 65 |

| Table 21 MTDC converter's variables                                                  | 66 |

| Table 22 MTDC line's variables                                                       | 66 |

| Table 23 RQ model settings for PSCAD                                                 | 70 |

| Table 24 Current peak reduction and limiting factor                                  | 72 |

# SUMMARY

The growth of electrical energy demand along with the  $CO_2$  reduction requirements enhance the demand of new electrical energy generation and transmission systems. In the last decades renewable energy generation systems have rise considerably to face this challenge, especially wind energy and, lately, offshore win energy systems.

High Voltage Direct Current (HVDC) transmission systems are very suitable to integrate bast renewable energy generation into the main AC grid, as they are especially appropriate for long distance and undergrown / underwater transmission systems. However, one of the main disadvantages of these transmission systems are the lack of commercially available direct current circuit breakers for fault clearings since there is not naturally current zero crossing and the rise rate and final value of the current is very high under fault conditions.

The integration of current limiters, especially superconducting resistive type current limiters, into these transmission systems are seen as a promising solution to cope with the fault current clearing phenomena. Thus, this project is oriented to the modelling of this device, superconducting resistive type current limiter, and the simulation of this device in a real HVDC multiterminal grid.

# RESUMEN

El aumento de la demanda de energía eléctrica junto con el requerimiento de reducción de emisiones de  $CO_2$  generan la necesidad de nuevas tecnologías de generación y transporte de electricidad. A lo largo de las últimas décadas las energías renovables han tomado un papel importante para enfrentarse a este reto, especialmente la energía eólica, y últimamente la energía eólica offshore.

Los sistemas de transmission de alta tension en corriente continua son muy apropiados para integrar grandes cantidades de energía eléctrica al sistema electrico de potencia, ya que son muy aptos para transmisión a larga distancia y transmisión subterránea y submarina. Si embargo uno de los principales inconvenientes es la falta de interruptores automáticos para corriente directa, ya que en estas aplicaciones no hay paso natural por cero y la corriente alcanza valores muy elevados muy rápidamente en condiciones de falta

La integración de limitadores de corriente, especialmente los de tecnología superconductora resistiva, son considerados como una solución prometedora a este problema. Este proyecto esta orientado al modelado de limitadores de corriente de tecnología superconductora resistiva y la simulación de una red HVDC multiterminal con este dispositivo.

# **1. INTRODUCTION**

Implementation of multiterminal high voltage direct current (MTDC) is seen as a key solution for the electrical energy demand increase and for integrating large scale renewable energies. Nevertheless, high voltage direct current (HVDC) technology is not mature enough to enable wide existence of this grids, and up to date most of the HVDC transmission systems are two-points lines.

One of the most challenging aspects of this technology is the fault clearing since DC currents have no zero crossing. One way to open the faulted circuit is to trigger the AC side breakers, however, this may lead to the full de-energization of the line or grid, making these systems unreliable, especially if overhead lines are desired.

Direct current circuit breakers are still under development, and they cannot withstand high current breaking capabilities, furthermore, due to the high rate of rise of the current, these devices must operate within few milliseconds, while in AC operate in several milliseconds.

Considering this, fault current limiters, limiting both rise rate and peak value, are of concern in this transmission systems. Several researchers have claimed the resistive superconducting fault current limiter as a promising solution for this technical limitation.

# **1.1 BACKGROUNG**

Power systems should provide reliable electrical energy generated by different technologies to different load types. Power systems are complex grids exposed to several types of faults, some of them transient and some others permanent. Most common fault types are short-circuiting, which are the non-desirable connection between to terminals at different potentials, which may result in high currents. Short circuit current is defined by the short circuit power and the voltage level of the system. A high  $S_{SC}$  means a strong grid in terms of power quality, but it leads to high  $I_{SC}$  values [1].

$$S_{SC} = \frac{U_{AC}^2}{Z_{TH}}$$

Equation 1

$$I_{SC} = \frac{S_{SC}}{\sqrt{3}U_{AC}}$$

#### Equation 2

Fault currents are feed by the followings [2]: 1) Synchronous generators connected to neighbour buses (especially permanent current), 2) Large induction motors (especially transient), and 3) distributed generation (DG).

In the last years, the distribution grid has experimented a huge increase in DG, especially from wind farms, leading to the increment of the system  $I_{SC}$ . The contribution of  $I_{SC}$  of the DG depends on the technology, for instance, a PV panel connected via inverter can saturate the output power to 2 times the nominal current, whilst a windmill based on DFIG (converter on the rotor side) may reach 6 times the nominal current. The main negative effects of short circuits are the followings:

- Power interruption

- Damped mechanical oscillations on the electrical machine's shaft

- Negative rotational inertia and stress on the damping windings of the synchronous machines

- Increase in reactive power demand in the line impedance and leakage impedance of transformers

- Voltage drop in buses with sensitive loads

- Torque reduction in induction machines and increased demand in reactive power

- Thermal stress on equipment

- Voltage swell in faulted buses and sag in un-faulted buses

- Electromagnetic interference

- Increased unsupplied energy and economic losses

- Corrosion in the connection area

- Reduction in power system reliability

- Mechanical stress on the structures

- Etc...

Consequently, there is a need to limit the  $I_{SC}$  if no oversizing of the tolerable fault current (TFC) of the elements of the systems is desired. This can be achieved by network level strategies or device level strategies [3]. According to device level strategies, the use of fault current limiters (FCL) is a good technique to reduce  $I_{SC}$ .

Fault current limiters are widely used in AC systems. However, its application in HVDC systems is promising, considering the HVDC system inherent response to faults.

### 1.1.1 Fault Current Limiters

FCL are devices with virtually zero impedance during the normal operation of the system, but when fault occurs, the impedance of the devices increases to the set value. The requirements for being a good FCL are the following [4]:

- It should have low impedance during normal operation

- It should limit the fault current withing a short period of time

- It should take a short time to recover

- The FCL should limit the current in case of device fail

- In some applications (for instance, offshore applications), it should be compact and light

- It should be easily scalable to high voltage applications

There are several types of FCL, but they can be classified in four groups:

- 1. Solid-State Fault Current Limiters (SSFCL)

- 2. Superconducting Fault Current Limiters (SFCL)

- 3. Hybrid Fault Current Limiters (HFCL)

- 4. Other technologies

The integration of FCL in a power system brings the following advantages [2]:

- The power system equipment in general can be designed with lower TFC

- The is no need for replacing the current limiting devices (not applicable for fuses)

- In steady state conditions FCL does not imply voltage drop nor harmonic injection

- Low power losses during normal operation

- Transient stability is improved

- Reduction on thermal stress

- Fast voltage reduction is avoided, voltage stability improved

- Fault ride through of loads and generators is improved

- Allows high level of network interconnection

- Favours DG integration

- Etc...

Withing all the FCL types, SFCL are the most used technology and specially the resistive type ones, as depicted in Figure 1.

Figure 1 FCL Types and number of installed devices in real power systems [2]

Figure 2 shows a comparison between the technical characteristics of the different types of FCL technologies.

| Parameters/FCL                   | SFCL                                   | SSFCL                      | HFCL                             | Other                     |

|----------------------------------|----------------------------------------|----------------------------|----------------------------------|---------------------------|

| Operating voltage                | 220 V-510 kV AC, 500 kV DC             | 150 V-500 kV AC            | 15 kV AC                         | 380 V-110 kV AC           |

| Rated current                    | a few amperes to 10kA                  | a few amperes to 3kA       | 2kA                              | a few amperes to 2kA      |

| Material technology              | superconductor                         | semiconductor              | superconductor and semiconductor | Low-impedance reactor     |

| Time response                    | 2.5 ms-10 ms                           | 1 µs to a few ms           | less than 1 ms to 2 ms           | Less than 2 ms            |

| Percent of transient overvoltage | 0.6%-2.3% (A4)                         | about 2% (A3)              | about 10% (A2)                   | 2.5%-20.5% (A1)           |

| weight                           | 3-36 tones                             | a few kg- a few tones      | from one to a few tones          | from a few kg to one tone |

| Physical dimensions              | The largest                            | The smallest               | fairly large                     | large                     |

| Cooling system                   | high power ratings, voluminous, liquid | heatsink, air ballast      | heatsink, air ballast, liquid    | air ballast, natural      |

|                                  | nitrogen                               |                            | nitrogen                         |                           |

| cost                             | the most expensive                     | the cheapest               | fairly expensive                 | expensive                 |

| Manufacturing as a compact pack  | No                                     | Yes                        | No                               | No                        |

| Modular                          | No                                     | Yes                        | No                               | No                        |

| Reliability                      | the most reliable                      | has the lowest reliability | reliable                         | fairly reliable           |

| Harmonic generation              | very low                               | very high                  | high                             | low                       |

| Loss                             | very low                               | low                        | high                             | very high                 |

| Voltage drop                     | very low                               | high                       | low                              | very high                 |

| No-load loss                     | very high                              | very low                   | low                              | high                      |

| Needs to maintenance             | high                                   | low                        | very high                        | very low                  |

Figure 2 Technical comparison between FCL technologies

The main advantages of the SFCL are the applicability to high voltage and currents, reliability, low harmonics, losses, and voltage drop. These characteristics make them appropriate for high voltage and power systems, such as HVDC.

#### 1.1.2 HVDC development

The increase of electrical energy demand after the second world war stimulated the research in high voltage direct current (HVDC) transmission systems, especially in Sweden and the

former Soviet Union. HVDC lines have been used for more than 60 years and offers advantages against conventional HVAC transmission systems depending on the applications and casuistry. The first commercial HVDC was built between the island of Gotland and Swedish mainland and was a 98km submarine cable with ground return, however, the first experimental HVDC line was built between Moscow and Kasira in 1950 and was a 116km length transmission line at 200kVdc [5].

The main reasons for using HVDC technology are the following ones:

An overhead DC line can be less costly per unit of length than an AC transmission system designed for transmitting the same amount of electrical power, furthermore, if very high voltages are achieved, the losses are decreased. However, DC converter stations are much more expensive, so there is a breakpoint at a determinate distance, as depicted in Figure 3. There are other environmental advantages as the electric and magnetic fields are in DC instead of AC.

Figure 3 HVAC vs HVDC cost comparison: (a) economical breakpoint (b) Cost and ROW estimation for 6000MW transmission line of 2000km [6]

- 2. If transmission system is underground or submarine this breakpoint moves substantially to the left, which is usually at 50km. This is due to the huge increase of stray capacitance of underground or submarine cables. Thus, this technology can help in the integration of large offshore wind farms and the interconnection with oil and gas offshore platforms.

- 3. Some AC electrical systems are not synchronized even though they are physically close to each other, as occurs in Japan where half of the country's network is at 50Hz and the other is at 60Hz. By interconnecting these networks by a DC link, power flow can be achieved.

According to HVDC, two main technologies can be distinguished: Voltage source converters (VSC) and line commutated converters (LCC). The choice of converter technology depends on the casuistry and application. VSC technology is claimed to be the best technology for implementing multiterminal HVDC grids due to the following advantages [7]:

- Independent and fast active and reactive power control

- Absence of harmonic filters

- Suppression of commutation failure

- Connection of passive AC loads

- Lower footprints

- Operation without telecommunication between terminals

- Capability of power reversal without voltage polarity reversal in DC side

# **1.2 OBJECTIVES OF MASTER'S THESIS**

The first objective of this master thesis is to evaluate the state of the art of HVDC systems, its main technological basis, grid configurations, fault phenomena and the applied circuit breakers operation.

The second objective is to evaluate the different superconducting resistive type of current limiter's models.

Finally, the main objective of this master thesis is to evaluate the HVDC grid response when a current limiter is integrated under fault conditions.

# 2. HVDC SYSTEMS

Over the last few years, there has been a huge increase in the cumulative HVDC power capacity. Figure 4 [6] shows the evolution of the cumulative HVDC system power in world, it can be noticed that in the last 15 years the growth has been exponential, specially due to China's projects.

Figure 4 Evolution of cumulative HVDC capacity

HVDC system suppliers is dominated by ABB, Siemens, and Alstom Grid (whose energy business was absorbed by General Electric in 2015).

According to HVDC systems, converter stations can be technologically divided in two; current source converters (CSC) or line commutated converters (LCC), using thyristor-type valves, and voltage source converters (VSC), using IGBTs. Historically, HVDC systems has used LCC, but the improvement in the semiconductors devices (especially IGBTs) and the development of the digital signal processing techniques allowed the development of this kind of converters for these applications.

First VSC project was commissioned in Gotland (50MW +/-80kV), nowadays there are systems up to 900MW and with rated voltage up to 320kV, as can be shown in Table 1. ABB claim to have reached levels up to 525kVdc with its VSC technology [8], as in Zhangbei HVDC grid [9].

| Projects   | Year | Converter<br>Type       | Power<br>Rating (MW) | Converter<br>Losses (%) | DC Voltage<br>(kV) | Supplier |

|------------|------|-------------------------|----------------------|-------------------------|--------------------|----------|

| Gotland    | 1997 | Two-Level               | 50                   | 3                       | <u>+</u> 80        | ABB      |

| Eagle Pass | 2000 | Three-Level<br>with PWM | 36                   | 2.2                     | ±15,9              | ABB      |

| Estlink    | 2006 | Two Level<br>PWM        | 350                  | 1.4                     | <u>+</u> 150       | ABB      |

| Trans Bay  | 2010 | MMC                     | 400                  | 1                       | <u>+</u> 200       | Siemens  |

| Cable      |      |                         |                      |                         |                    |          |

| Nan'ao 3-  |      |                         |                      | -                       |                    |          |

| terminal   | 2013 | MMC                     | 200/100/50           |                         | ±160               | Multiple |

| DC grid    |      |                         |                      |                         |                    |          |

| SW Link    | 2014 | MMC                     | 2x720                | -                       | <u>+</u> 300       | Alstom   |

|            |      |                         |                      |                         |                    | Grid     |

| Dolwin2    | 2014 | MMC                     | 900                  | -                       | <u>+</u> 320       | ABB      |

#### Table 1 HVDC projects evolution

Up to date, the largest commissioned line, based on LCC, is a 1100kVdc 12GW line of more than 3000km in China. It is a clear example of the usefulness of this technology as it is conceived to integrate the large amount of surplus renewable energy generation of the bast northwest of China into the more populated zones in east [10].

The selection of a LCC or VSC technology depends on the application and casuistry. Table 2 shows the attributes for each technology type [11]:

| Function                                     | LCC                          | VSC                                         |  |

|----------------------------------------------|------------------------------|---------------------------------------------|--|

| Thyristors, currently up to                  |                              | IGBTs with anti-parallel freewheeling       |  |

| Semi-Conductor 8.5kV and 5000Amps. Not       |                              | diode, with controlled turn-off capability. |  |

| Device                                       | controlled turn off          | Current voltage rating 4.5 to 6kV and turn  |  |

|                                              | capability                   | off current of 120Amps                      |  |

|                                              | Up to +/- 800kV bipolar      |                                             |  |

| <b>DC Transmission</b>                       | operation, 1000kV under      | Up to +/-320 kV to 400 kV                   |  |

| Voltage                                      | consideration in China       |                                             |  |

|                                              | Currently in the range of    | Currently in the range of 600 to 1000 MW    |  |

| DC power                                     | 6000 MW per bipolar          | per pole                                    |  |

|                                              | system                       |                                             |  |

| <b>Reactive Power</b>                        | Consumes reactive power      | Reactive power controllability              |  |

| <b>Requirements</b> up to 60% of its ratings |                              |                                             |  |

| FilteringRequires large filter ban           |                              | Requires moderate size filter banks or no   |  |

|                                              |                              | filters at all                              |  |

| Black start Limited applicatio               |                              | Capable of black start and feeding passive  |  |

|                                              |                              | loads                                       |  |

| Commutation                                  | Fails commutation for ac     | Does not fail commutation                   |  |

| failure                                      | disturbance                  |                                             |  |

| performance                                  |                              |                                             |  |

| Overload                                     | Available if designed for up |                                             |  |

| capability                                   | to any required design       | Does not have any overload capability       |  |

|                                              | value                        |                                             |  |

|                                              |                              | Can be applied but DC line faults are       |  |

| Applications with                            |                              | cleared by trip of AC breaker, or the use   |  |

| overhead lines                               |                              |                                             |  |

|                                                                                         | Can be applied and dc line<br>faults can be cleared by<br>converter control    | of a dc circuit breaker. It has mostly been<br>applied with cables |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------|

| Small taps                                                                              | ps Not economic and affects Economic and seems not the performance performance |                                                                    |

|                                                                                         |                                                                                | Not large because of small size of filters if required             |

| Footprint Can be large                                                                  |                                                                                | Small for the comparable rating to a LCC                           |

| Offshore wind<br>farmsCan be applied with some<br>dynamic voltage controlStraight forwa |                                                                                | Straight forward application                                       |

| Power Losses                                                                            | Typically, 0.8% per<br>converter station rated<br>power                        | Typically, 0.8 to 1% per terminal with multilevel converters       |

| Table 2 Comparison between LCC and VSC technol | ogy |

|------------------------------------------------|-----|

|------------------------------------------------|-----|

# 2.1 Converter technology

This chapter will summarise the main differences between LCC and VSC converter stations.

### 2.1.1 Line Commutated Converters

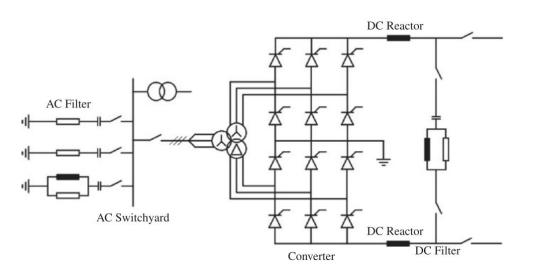

Figure 5 shows the basic elements for LCC technology [12]:

- AC filters: These filters minimize the main AC harmonics (passive resonant shunt filters) and compensate the reactive power

- Three winding Y/Y-D transformer: Provides galvanic isolation and generates 30 degrees shifted 3 phase systems needed for the 12-pulse converter operation

- 12 Pulse Converter: Rectifies AC to DC minimizing the harmonic generation

- DC filters: Composed by smoothing inductances and passive shunt filters

- Other components: Earthing electrodes, protection devices...

Figure 5 Schematic view of LCC-HVDC system

These systems are characterized by their robustness and high-power transmission capability. However, there is no controllability of the AC reactive power (it consumes) and the harmonic content is big, so there is the need for huge filters in AC and DC.

Furthermore, in LCC systems, a big short-circuit-ratio (SCR) is needed.

$$SCR = \frac{S_{SC}}{P_{DC}_{HVDC}}$$

Equation 3

$$S_{SC} = \frac{U_{AC}^2}{Z_{TH}}$$

#### Equation 4

This is due to the big amount of reactive power that is demanded by the converter and the effect of the SCR in the controllability of the DC link. The control of the HVDC link has an important impact on its interaction with de AC system.

The short circuit ratios can be classified as:

| High     | $\rightarrow$ | SCR > 5     |

|----------|---------------|-------------|

| Moderate | $\rightarrow$ | 3 > SCR > 5 |

| Low      | $\rightarrow$ | SCR < 3     |

| Very Low | $\rightarrow$ | SCR > 2     |

#### 2.1.2 Voltage Source Converter

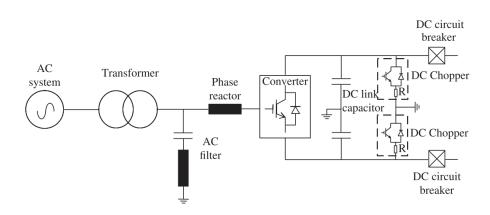

Figure 6 show the main components for VSC technology [12]:

- Transformer: Although it is not compulsory for the correct operation of the system, galvanic isolation is desired

- AC filter and phase reactor: Minimises the harmonic propagation through grid

- Converter: The trickiest component, rectifies AC signal by IGBTs commutating at high frequencies.

- DC capacitors: These capacitors are needed to stablish the voltage in the DC link.

- DC chopper: Its main function is to dissipate energy whenever is needed.

Figure 6 Main components of the VSC-HVDC system

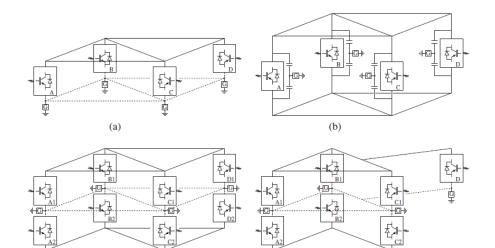

The converter topology can vary; it can be two level converter, or multilevel converter. Two level converters are the less complex ones but generates high harmonic content and they have higher losses due to the need of high frequency commutation. Multilevel converters can be divided in neutral point clamped technology (NPC) or modular multilevel converters (MMC). According to NPC, theoretically they can have 3, 5, 7 and higher levels, but the complexity of

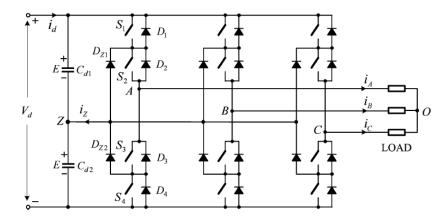

the converter increases drastically with the level increment, so for these applications only 3 level converters have been commissioned, as the shown in Figure 7.

Figure 7 Conventional 3-Level neutral point clamped converter [13]

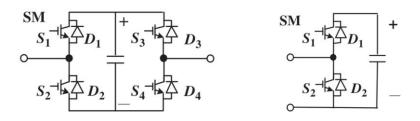

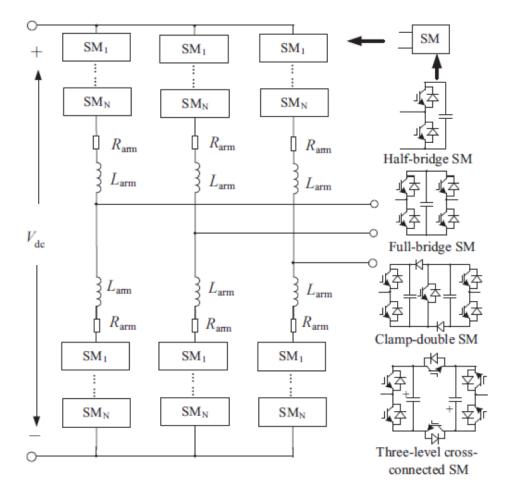

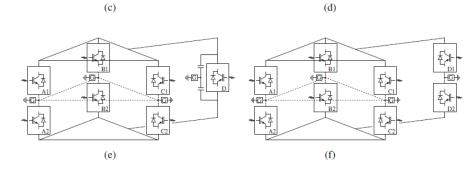

MMC converters may have much higher levels by serialising sub-modules (SM) as it is depicted in Figure 9 [14]. This SM can be made by different topologies, however, the most employed ones are half-bridge of full-bridge, as the ones showed in Figure 8.

Figure 8 Most used SM topologies: Full-Bridge (Right), Half-Bridge (Left)

Half-bridge sub-module only offers two levels (Vdc o zero) while full-bridge topology offers three levels (Vdc, zero and -Vdc). This implies the main two following advantages:

- More Voltage levels with same SM number [13]

- AC infeed blocking capability [12] (as does the Alternate-Arm Converter, which is not treated in this document). This can be achieved by inserting an opposite voltage in AC side.

MMC converter topology offers more voltage levels (better harmonic content) with low commutation frequency at SM level (low losses and HF noise). Moreover, the smoothing reactance's in AC and DC limit the raising rate of current in case of fault. However, the complexity relapses in the individual control required for the SM and the number of independent capacitors.

#### Figure 9 Schematic of MMC

Table 3 compares the attributes of the VSC different topologies for HVDC:

| TWO-LEVEL CONVERTERS           | MULTILEVEL CONVERTERS                |  |

|--------------------------------|--------------------------------------|--|

| Series-connected IGBTs and PWM | Multi-modular in cascaded connection |  |

| Conceptually simple circuit    | Easily scalable                      |  |

| Requires PWM                   | More complex controls                |  |

| High switching losses          | Low switching losses                 |  |

| Harmonic problems from PWM     | Virtually no harmonics               |  |

Table 3 Comparison between two-level and multilevel converters fod HVDC applications

From now on, it is only going to be considered VSC technology as is the most appropriate for MTHV.

# 2.2 Configurations and introduction to HVDC grids

Most of up to date HVDC systems are point to point [15]. However, the use of MTDC may provide the following advantages compared with a conventional HVDC transmission system between two points [4]:

- Improve reliability of the DC link

- Better handling of the intermittent nature of renewable generation

- Maximize use of converters

Table 4 shows actual projects of MTHV in China [6].

| System<br>Name | Terminals | Rated Power (MW)            | Rated Voltage<br>(kV) | Status                 |

|----------------|-----------|-----------------------------|-----------------------|------------------------|

| Nan'ao         | 3         | 200 / 100 / 50              | <u>±</u> 160          | Commissioned<br>(2013) |

| Zhoushan       | 5         | 400 / 300 / 100 / 100 / 100 | ± 200                 | Commissioned<br>(2014) |

| Zhangbei       | 4         | 3000 / 3000 / 1500 / 1500   | ± 500                 | Under Construction     |

#### Table 4 MTHV projects in China

This chapter will introduce the basics to understand the HVDC system configuration and grids.

### 2.2.1 System configuration

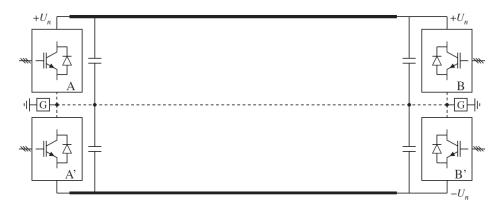

There are three basic configurations according to VSC; asymmetrical monopole, symmetrical monopole, and bipolar configurations [12].

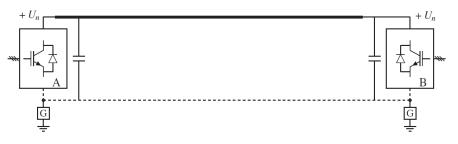

Figure 10 [12] shows an asymmetrical monopole configuration, where a three-phase connection is to the DC converter midpoint, and in the DC side one pole is grounded. The current return can be done by a metallic neutral conductor or by ground where high ground currents are allowed. In case of a metallic return, the cable must be size for the total current, but lightly insulated. This configuration is the simplest one, but the disadvantages are that the transformer must withstands constant DC component and a failure in the high voltage cable leads to the complete disruption of the line.

Figure 10 Asymmetrical monopolar configuration

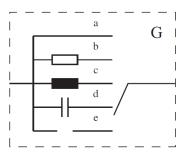

The symbol G corresponds to the grounding, which can be done as shown in Figure 11 [12]. The grounding of the system can be done by direct grounding (a), resistive grounding (b), inductive grounding (c), capacitive grounding (d) and high impedance grounding (e). High impedance grounding is usually employed as fault currents are minimized with this configuration.

Figure 11 Grounding options

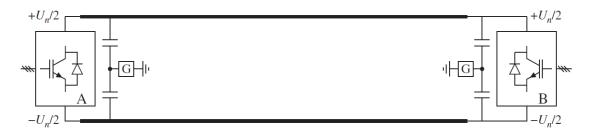

Symmetrical monopolar configuration is showed in Figure 12 [12]. The AC connection is made in the same way, but the two terminals of DC link are connected to two poles working with the same voltage level but in opposite sign. These poles must be rated to the duty current and full voltage. As DC voltage is symmetrical, the transformer does not experiment any DC voltage. The grounding can be done by connecting the midpoint of the DC bus to ground by a high impedance.

Figure 12 Symmetrical monopolar configuration

In case of pole to ground fault, the healthy pole can reach theoretically  $U_n$ , this must be considered for the insulation design of both poles. This configuration is widely used in VSC-HVDC. The loss of one converter or line leads to the disruption of the whole power transmission.

By last, Figure 13 [12] shows a bipolar configuration, by connecting two asymmetrical monopoles sharing ground and metallic neutral conductor. Its converter has its own transformer and can operate independently. In normal operation, no current flows through the metallic return path. In case of one converter failure, the return is made by the metallic path ensuring the 50% of power transmission.

Figure 13 Bipolar configuration

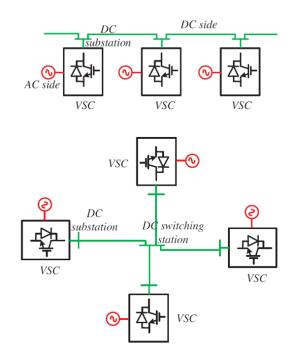

# 2.2.2 HVDC grids

According to HVDC grids, they can be distinguished as radial topologies and meshed topologies. Radial topologies can be composed by strings or stars, as depicted in Figure 14 [12].

Figure 14 Radial topologies; String composition (up), star composition (down)

While meshed topologies can by created by the union of two or more radial topologies or by a real meshed grid composed by several nodes, as shown in Figure 15 [12].

Figure 15 Meshed topologies

BILBOKO INGENIARITZA ESKOLA ESCUELA Euskai Herriko Unibertsitatea DE BILBOO

Universidad del País Vasco

More detailed multiterminal grids, considering the possible configurations, are shown in Figure 16. Some possible HVDC grids could be (a) Asymmetric monopolar grid with earth return, (b) Symmetric monopolar grid, (c) Bipolar grid with metallic return, (d) bipolar grid with metallic return and asymmetric monopolar tapping, (e) bipolar grid with metallic return and symmetric monopolar tapping, (f) bipolar grid with metallic return and bipolar tapping with earth return.

Figure 16 Possible HVDC grids

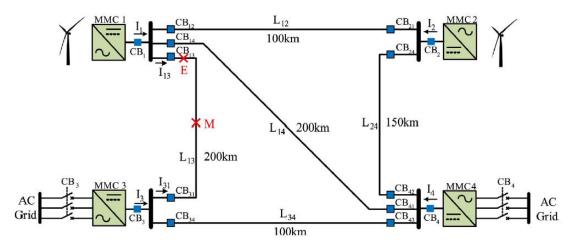

Figure 17 shows one of the typical case study multiterminal HVDC meshed grid, which interconnects offshore wind farms with mainland AC systems.

Figure 17 Four terminal HVDC meshed real grid [16]

This grid configuration could be considered as a real HVDC grids as if offers redundancy, meshed connections, and circuit breakers to isolate faulted lines.

The parameters of the grid are shown in Table 5:

| Parameter                               | Conv 1,2,3   | Conv 4       |

|-----------------------------------------|--------------|--------------|

| Rated Power [MVA]                       | 900          | 1200         |

| AC grid voltage [kV]                    | 400          | 400          |

| Converter DC voltage [kV]               | <u>+</u> 320 | <u>+</u> 320 |

| Arm capacitance $C_{arm}$ [uF]          | 29.3         | 39           |

| Arm reactor <i>L<sub>arm</sub></i> [mH] | 84.8         | 63.6         |

#### Table 5 MTDC grid parameters

The main impediment for the MTDC development is the lack of appropriate direct current circuit breakers for high voltage and current levels.

# 2.3 HVDC Faults

As every power system, HVDC grids are exposed to faults, especially in overhead lines. DC protection systems must fulfil the same objectives as AC protection [17].

- Detect and isolate the faulted line, equipment, or installation

- Detect and alarm about the undesirable situations in lines, equipment, or installations

- Detect and alarm about the abnormal situations in lines, equipment, or installations

The requirements of a DC protection systems are the same as the AC ones:

- Sensitivity: Capability of being able to operate under the minimum fault condition

- Selectivity: Capability of being able to distinguish the faults when the protection device must act, so the smaller number of protection devices is tripped.

- Speed: This is essential for minimizing the hurt provoked by the fault in the protected equipment.

- Reliability: Grade of reliance of the protection device.

DC faults are characterized for the high rate of rise, large steady state value and no zero natural zero crossing, furthermore, power electronic components might suffer irreversible damages. Considering all this, the fault clearing time lies in the order of milliseconds ( < 5ms), comparing with the relatively large clearing time in AC system (2-3 grids cycles) due to the exploitation of the natural zero crossing.

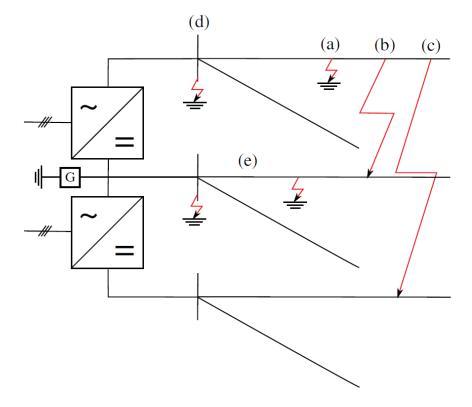

The prospective steady-state DC fault current is mainly determined by fault type and system grounding and configuration. The main DC faults can be classified as following [12]:

- Pole to ground faults (a)

- Pole to neutral faults (b)

- Pole to pole faults (c)

- Bus faults (d)

- Neutral to ground faults (e)

Figure 18 [12] illustrates the placement of each fault type in a HVDC system. The most common faults are pole to ground and pole to pole.

#### Figure 18 DC Fault types

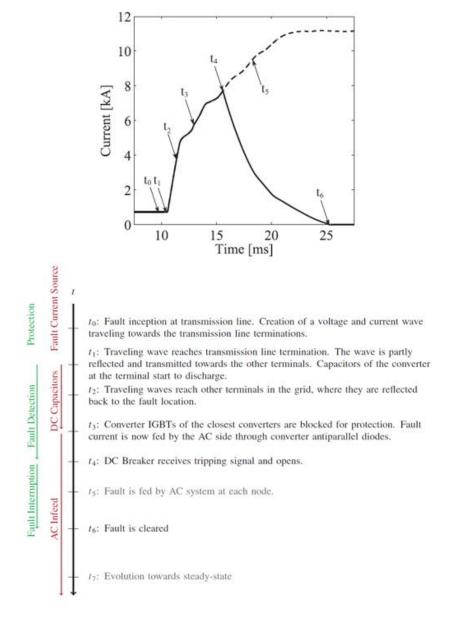

Figure 19 [12] shows an example of DC fault in HVDC grid. The system response can be evaluated as a DC switched voltage to a RL circuit, which is characterized by the steady state prospective current  $U_{dc}/R_{line}$  and the transient rise is determined by the time constant  $\tau = L_{line}/R_{line}$ . Figure 20 [12] shows the current during the fault and all the events until the fault is cleared by the protection system (PS).

Figure 19 Fault in HVDC grid

#### Figure 20 Events during DC fault

When, for instance, a solid pole to ground fault occurs, the voltage decreases from  $U_{dc}$  to zero, but this decrease is not measured instantaneously at the line end, this is due to the travelling wave phenomena. The travelling wave speed is dependant of the inductance and capacitance of the line, as is the characteristic impedance. The propagation speed for overhead lines and cables is around the speed light (approximately  $3 \cdot 10^8 m/s$ ) and half of the speed light, respectively.

$$Z_{c} = \sqrt{\frac{L}{C}}$$

Equation 5

$$v = \frac{1}{\sqrt{LC}}$$

**Equation 6**

Once the wave has reached the line end, this voltage drop is seen in the terminals and the converters connected to that terminal starts feeding the faults. Part of this wave is reflected to the same line and the other part travels through the other terminals of the HVDC grid, and the other converters connected to the grid will feed the fault as the travelling wave reaches them.

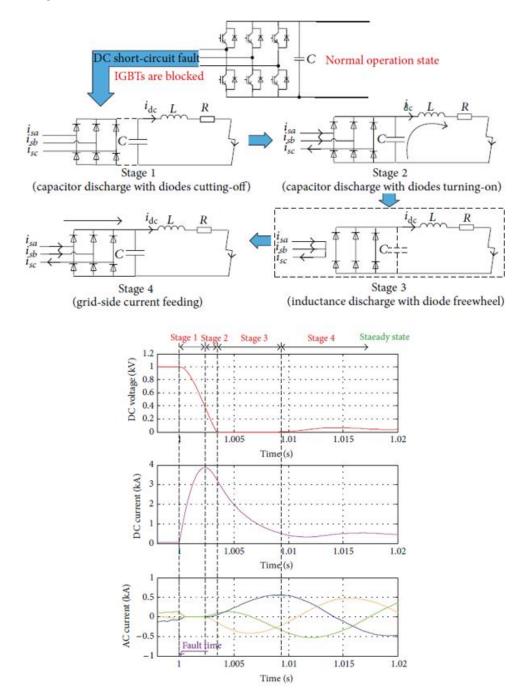

Once analysed the behaviour of the line, analysis on the converter must be done, as it is the fault feeding element. Figure 21 show the behaviour of the converter, which is characterized by four stages.

Figure 21 Behaviour of the VSC during DC faults

For simplifying the analysis, a schematic of a two level VSC is shown, however, there are several scientific papers explaining the behaviour of other, and more complex, converters, such as MMC (half-bridge or full bridge) and three level NPC.

As soon as the current passes the current threshold, which is usually two times the nominal current, the IGBTs are blocked for avoiding damaged due to thermal stress. The first and second stage are characterized by the discharge of the capacitors, which provides a large current. Once the capacitor voltage is below the peak AC voltage value, the diodes get polarized and the AC side starts feeding the fault, as does the capacitor. When the capacitor is fully discharge, only the AC side feeds the fault and the converter behaves like a rectifier with an extremely high load, this is, extremely low resistance in parallel with the capacitor. Voltage measured in converter's terminals will be:

$V_{fault} = I_{fault} \cdot Z_{fault}$

**Equation 7**

# 2.4 Direct current Circuit Breakers

One of the main barriers against the development of VSC based MTHV is the high vulnerability to short circuit.

DC fault interruption process is much more complex that the interruption of AC fault current. Conventional AC circuit breakers interrupt the current with the help of natural zero crossing, which does not exist in DC systems.

Moreover, due to the small impedance of the DC system, DC fault current is characterized by high steady state value and rise rate, as stated above in this chapter. Considering this, direct current circuit breakers (DCCB) must open fault current in few milliseconds.

Two-point HVDC transmission line can cope with short circuiting by opening the AC side breakers and de-energizing the whole line, however, this is not desirable for MTHV as the whole system must be de-energized.

This leads to demand of a development of direct current circuit breakers (DCCB) which differs from the AC ones. The acceptance of HVDC networks regarding efficiency, reliability and controllability will strongly depend on the availability of HVDC circuit breakers.

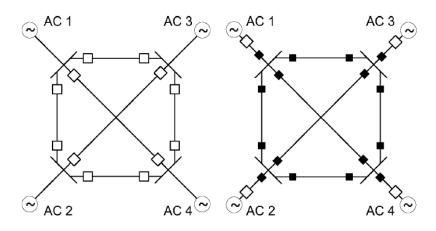

In principle, it is possible to connect many AC nodes to one point generating a so-called multiple-pair configuration as is depicted in Figure 22 [15], where black boxes are DCCB and white boxes are converters. However, there are several advantages by connecting the nodes on DC side [15], as in the right side of Figure 22:

- Number of converter stations could be reduced, significantly reducing the cost and the losses of the total system

- Each station can transmit power individually and can even change from receiving to sending power without requiring that the opposite converters does so

- There is more redundancy and lines can be decoupled individually, maintaining the converters in normal operation.

Figure 22 Comparison of point-to-point system grid (left) and real MTDC (right)

Nevertheless, DCCB for high voltage are not commercially widely available today. The main requirements for DCCB are the following ones [18]:

- Create a zero-crossing current to interrupt it (case of conventional hybrid and mechanical)

- Very fast breaking action (due to the high rate of rise)

- Minimal conduction losses (and voltage drop)

- Reliable protection

- Prevent excessive overvoltage

- Minimal arcing

- Provide enough isolation capability to system rating

- Long lifetime

- Less maintenance and, in case, capability to bypassing the current to prevent service interruption

Direct current circuit breakers are usually composed by three parallel paths: the nominal current path, commutation path and energy absorption path. According to DCCB technology, there are mainly three types:

- 1. Mechanical circuit breakers (M-DCCB)

- 2. Solid-State circuit breakers (SS-DCCB)

- 3. Hybrid technology circuit breakers (H-DCCB)

### 2.4.1 Mechanical DC circuit breakers

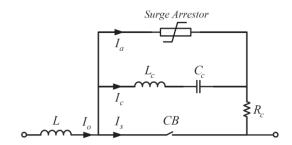

Passive mechanical CB are divided in two groups depending on how they create the zero crossing. This zero crossing can be generated by passive or active current injection.

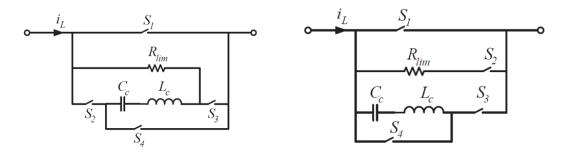

Passive mechanical CB was the first technology developed and was thought for LCC converters. Figure 23 [18] shows the schematic of a M-DCCB, when a fault occurs CB is opened, and the current is commutated to the commutation path. The spark created by the opening of the CB of the nominal current path triggers the resonance between  $L_c$  and  $C_c$ , DC current is superposed to the resonant current until the amplitude is high enough for creating a natural zero-crossing. This zero-crossing is enough for interrupting the current, however the clearing time is about 60ms, which is very high.

Figure 23 Passive resonant mechanical CB

According to active current injection M-DCCB, Figure 24 [18] illustrates the first (left) and second (right) variants of this technology. The main difference with the former M-DCCB is that the zero crossing is generated with a pre-charged capacitor,  $C_c$ , discharging through an inductance,  $L_c$ .

Figure 24 Active resonant mechanical CB

According to first generation topology, when an ordinary operation only  $S_1$  is closed, but when a fault occurs,  $S_1$  opens and immediately  $S_2$  and  $S_3$  closes generating a zero crossing through the commutation path.

### 2.4.2 Solid State DC circuit breakers

Fast and ultra-fast switching time of semiconductor devices make them very strong candidate for DC fault interruption. This technology is the fastest amongst the DCCB. In pure SS-DCCB IGBTs or other semiconductor are series-parallel connected to support voltage and current during normal and fault condition.

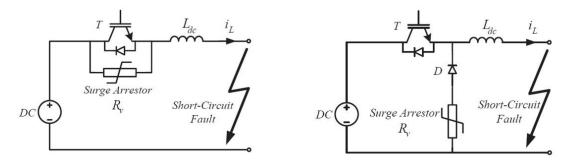

Figure 25 Solid-State CB

Figure 25 [18] shows the first (left) and second (right) topologies of SS-DCCB. In both topologies, T is opened as soon as the fault is detected, and the energy stored in the system

inductance is discharge in the surge arrester. In the second topology, due to the free-wheeling diode, the dissipating capability of  $R_v$  is reduced.

### 2.4.3 Hybrid technology DC circuit breakers

By integrating solid-state devices in a mechanical CB many advantages can be achieved. Recent developments in semiconductor technology such as break-down voltage, conduction losses, switching time and reliability allows the integration of this devices with mechanical pure CB. This combination is traduced in a faster operation than classical M-DCCB with lower operation losses compared with the SS-DCCB.

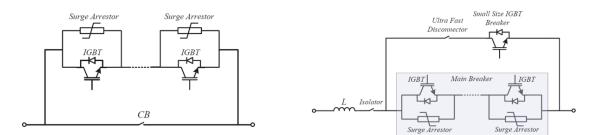

Figure 26 First topology (left) and second topology (right) hybrid circuit breaker

Figure 26 [18] shows the two main topologies for hybrid circuit breakers. During normal operation, current flow through the bypass, this is, ultra-fast disconnector (UFD) and small size IGBT breaker. When DC fault occurs, auxiliary breaker commutates and UFD opens, commutating current to the parallel branch. When this occurs, the main breaker opens and the UFD is exposed to the voltage defined by the protective level of the arrester.

### 2.4.4 Comparison

Nowadays DCCB technology has many limitations for being considered fully appropriate for a reliable and cost effective MTDC protection. Table 6 [19] compares the main attributes of each DCCB technology.

| Feature               | Active M-DCCB | SS-DCCB | H-DCCB    |

|-----------------------|---------------|---------|-----------|

| Internal current      |               |         |           |

| commutation time      | < 5 - 8       | 0.4     | 2 - 3     |

| (ms)                  |               |         |           |

| Interruption          | 2 - 10        | 19      | 7.5 - 16  |

| capability (kA)       |               |         |           |

| Voltage rating (kV)   | < 400         | 132     | 320       |

| On-state losses       | Negligible    | High    | Low       |

| Rate of rise of fault | 1.6 - 2       | 47      | 2.9 – 6.7 |

| current (kA/ms)       |               |         |           |

| Installation Costs    | Low           | High    | High      |

| Maintenance           | Required      | Low     | Required  |

#### Table 6 Comparison between DCCB tehcnologies

There are no DCCB that meet all the desired requirements. Many future research needs are detected in [15], such as the combination of circuit breakers with current limiters.

The use of high voltage current limiters is stated as one promising solution to cope with the troublesome of the fast-clearing time and current breaking capability.

Specifically, current limiting reactors and resistive type superconducting current limiters in operation with circuit breakers can adjust the response of the system favourably to the maximum breaking capacity and clearing time.

# 2.5 HVDC grids and protections

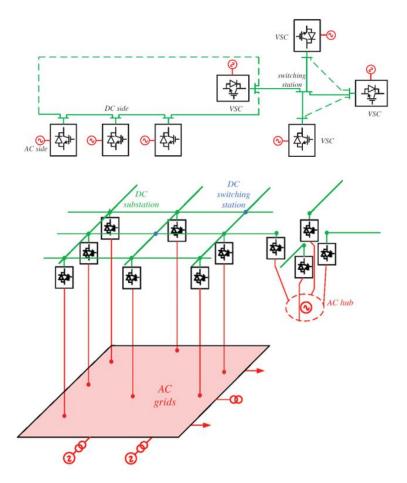

As mentioned in the document, HVDC multiterminal systems imply the necessity of fast and high current-voltage capability DCCB, in this section real examples HVDC grids and their implementation of CB breakers are going to be discussed as well as one proposal with R-SFCL.

# 2.5.1 Real example HVDC grids and protections

As showed in Table 4, up to date there are three multiterminal systems in China.

### 2.5.1.1 Zhoushan Multiterminal System

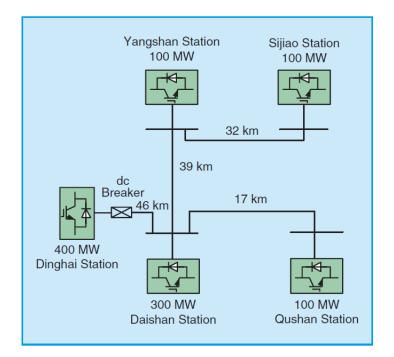

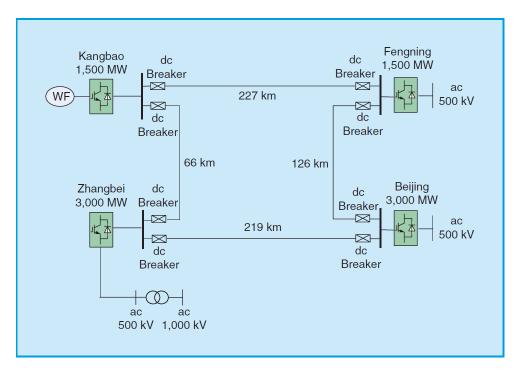

Figure 27 [20] shows the MTHV of Zhoushan archipelago, rated to  $\pm$ 200kV, which began commercial operation in 2014. The annual power load of Zhoushan is expected to reach 2000MW this year (2020) due to the economic development of China.

Figure 27 Diagram of Zhoushan archipelago five-terminal HVDC transmission grid

Originally, the faults were cleared by the slow operation of the ac side breakers, which result in many technical problems. In 2016, to improve the grid's reliability, security and efficiency, a hybrid CB rated 200kV with 15kA breaking capability was installed.

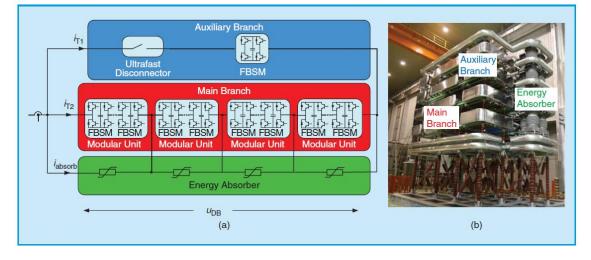

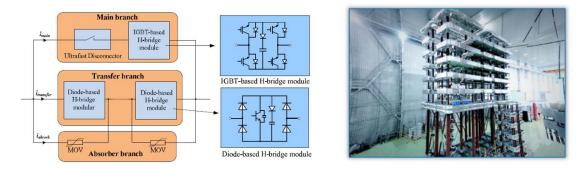

Figure 28 [20] shows the installed H-DCCB prototype, which is composed of:

- 1- Nominal current branch containing an UFD and a full-bridge submodule (FBSM)

- 2- Main interrupting branch containing 36 FBSM

- 3- Energy absorber branch to limit the transient voltage

Figure 28 a) Topology b) prototype of the hybrid circuit breaker

The H-DCCB passed the test in which a 15kA short circuit current was interrupted in 3ms with a transient interruption voltage of 320kV.

## 2.5.1.2 Nan'ao Multiterminal System

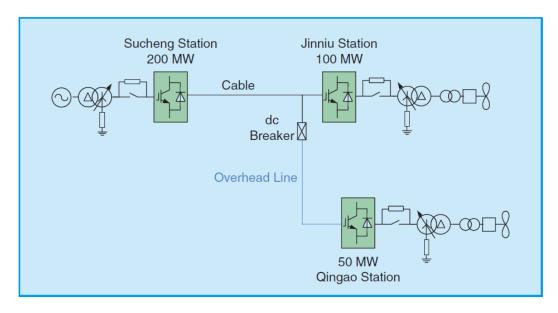

Nan'ao multiterminal system, with a  $\pm 160$ kV rated voltage, was put into operation in 2013. The original strategy for fault clearing was the same one as in Zhoushan. Thus, the project was upgraded in 2017 by adding a mechanical circuit breaker with active current injection. The M-DCCB was installed in the overhead line between Jinniu Station and Qingao Station, as shown in Figure 29 [20], as the overhead lines are more propense to faults.

Figure 29 Diagram of Nan'ao three terminal HVDC grid

The installed prototype 160kV M-DCCB consist of the following elements

- 1- Main branch with four 40kV rated vacuum interrupters. The voltage across these devices is balanced by adding parallel resistances and capacitances, as shown in Figure 30 [20].

- 2- Current injection is made by an auxiliary low voltage circuit. The unstoppable power supply (UPS) charges the capacitance through and current limiting resistances and a

halfwave rectifier (single diode). When fault occurs, the capacitance is discharge through the transformer that acts as inductance (leakage inductance) and provides galvanic isolation

3- The energy absorber consists of a bank of surge arresters (metal oxide varistors)

Figure 30 a) Topology b) prototype of the M-DCCB

Compared to conventional M-DCCB, this prototype is less costly and more compact due to the low voltage current injection auxiliary circuit. Experimental results show that the M-DCCB successfully interrupted 9,2kA fault current with a peak transient voltage of 272kV in 3,9ms.

#### 2.5.1.3 Zhangbei HVDC grid

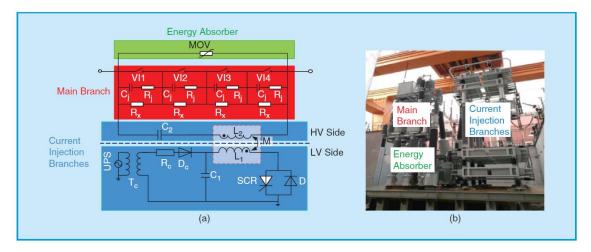

Zhangbei region in northern China has housed many wind projects in the last years and it is expected to grow its installed wind power at least up to this year. However, this wind generation is far from the high consuming points, moreover the variability of wind generation imposes challenges to the proper integration of this electricity into the grid.

Figure 31 Diagram of four terminal grid of Zhangbei

This can be addressed with the implementation of a multiterminal grid with correct placement of circuit breakers. Thus, a  $\pm$ 500kV, 3000MW four terminal grid was commissioned as the one shown in Figure 31 [20]. Fengning substation is connected to a pumped storage hydro plant, which can even out the fluctuations of wind power.

The project is considered as the first real HVDC grid in world as it has a proper positioning of CB which ensure efficiency and reliability and offers redundancy.

The circuit breakers were developed in 2018. Figure 32 [9] show the H-DCCB implemented in both ends of each line.

### Figure 32 a) Topology b) Prototype of H-DCCB

It has a 535kV rated voltage with 25kA breaking capacity. Breaking time is < 3ms and it can withstand 800kV in open state.

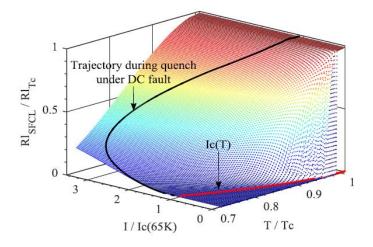

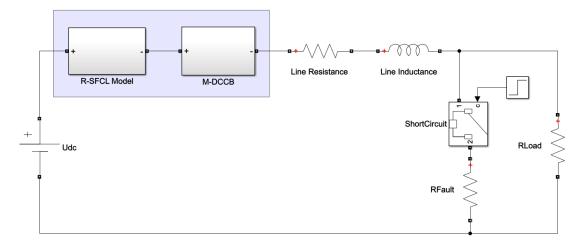

### 2.5.2 Proposed protection scheme

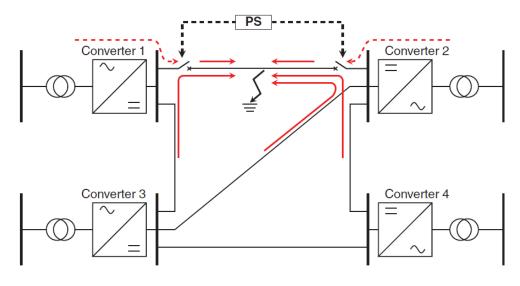

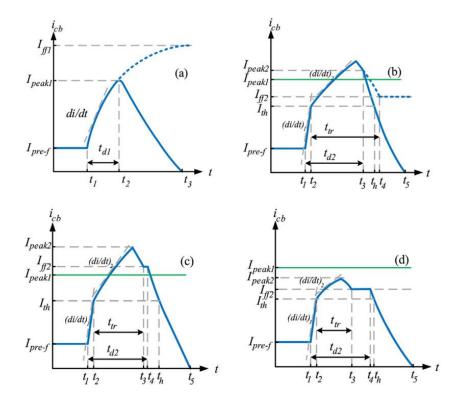

In [16] the system response is evaluated when a R-SFCL device is add together with a DCCB. Figure 33 [16] shows the evolution of the fault current in different scenarios, depending on the systems parameters, such as fault location, line inductance and CB opening time.

The following assumptions are considered:

- Equal circuit breaker interruption time for systems with and without SFCL

- Having less current limiting inductance with SFCL than in the system without SFCL (Reduction of this element is one of the expected advantages)

In a) the response without SFCL is depicted (less di/dt than other cases). In b) the response with a SFCL is depicted, but the transition time is longer than the CB operating time and di/dt is big enough (due to less inductance) for reaching higher current values that the a) case. In c) the transition time of SFCL is shorter than CB operating time, but still transition time is long enough and the developed resistance is small enough for reaching higher values that a) case. Therefore, it can be concluded that b) and c) cases are undesirable.

Desired system response is depicted in d), where the transition time is fast enough for limiting the current (small time with big di/dt) and the developed resistance is high enough to limit the value under  $I_{peak1}$ .

As mentioned above, this response depends on system characteristics, but also in SFCL device characteristics, so this analysis should be considered for designing an appropriate SFCL for each system.

Figure 33 Fault current evolution in different scenarios

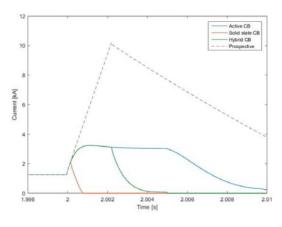

In [19], M-DCCB (active injection), SS-DCCB and H-DCCB performance are evaluated with the combination of a current limiting reactor (CLR) and a R-SFCL.

Figure 34 shows the fault currents of all scenarios evaluated in [19], it can be concluded that, firstly, the integration of R-SFCL limits substantially the fault current. Secondly, superconducting SS-DCCB have the smallest maximum current. By last, the maximum current with active injection M-DCCB and H-DCCB is the same.

This is because the current has reached the maximum value  $U_{dc}/R_{dc}$  when the M-DCCB and H-DCCB operates, whilst the clearing time of SS-DCCB is small compared even to time constant  $\tau = L_{dc}/R_{dc}$  of the faulted circuit and operates before reaching the steady state fault current value.

Figure 34 Currents for all scenarios

It can be concluded that the main benefit of the R-SCFL is that the response of M-DCCB and H-DCCB are equalized as more clearing time does not imply higher currents. A similar scenario as

the one depicted in Figure 33 d) is achieved, where the developed resistance limits substantially the current, and the transition time is short enough.

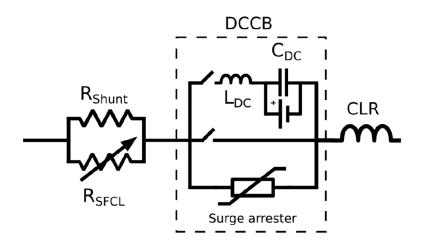

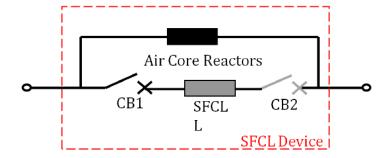

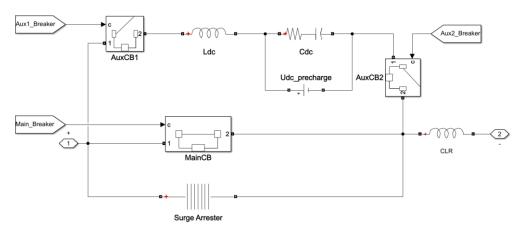

Figure 35 Superconducting M-DCCB with CLR

Furthermore, considering Table 6, it can be concluded that the best choice under the employment of a R-SCFL could be the active injection M-DCCB in series with a CLR, as the one depicted in Figure 35 [21].

# 3. STATE OF THE ART OF R-SFCL

Superconductivity was first discovered in 1911, when it was observed that some materials loss their electrical resistance at temperatures near absolute zero (4K). In 1986, high temperature superconductivity (HTS) was discovered by observing that some materials offer the same superconducting properties as the former ones, but at much higher temperatures around 70K [3]. In 2020, a research team of the University of Rochester claimed to have created a superconducting material at room temperature, this material is mainly composed by carbonaceous sulfur hydride which show superconducting attributes at 284,5K [22]. Materials with no electrical resistance are very interesting for power system applications.

Another interesting characteristic of the superconducting materials is the Meissner effect. Meissner effect is the repulsion of the magnetic field, this characteristic can be used for magnetic levitation.

Superconducting materials are used for the so called "bullet-train" allowing them to levitate and achieving speeds up to 600 km/h being almost impossible to derail [23]. These materials are also considered key element for allowing the nuclear fusion, where powerful electromagnets are needed so the plasma can levitate using the less amount of energy [24].

According to power system applications, four main promising applications can be distinguished [25]:

- Superconducting Cables: Superconducting cables allow low losses in power transmission. Nowadays most HTS cables are projected to AC system, DC HTS cables are in early stage but with promising results.

- 2. Superconducting Magnetic Energy Storage: Energy storage is important for allowing renewable energies integration and for power quality issues. These devices allow the storage of magnetic energy in a superconducting coil with low losses.

- 3. High Conducting Superconducting Generators: These generators have extremely highly efficient ratios and are very compact. These properties make them very appropriate for offshore wind farm applications where weight is crucial.

- 4. Superconducting Fault Current Limiters: Superconducting fault current limiters provide one of the most promising solutions for limiting currents. Compared with other technologies, they have negligible losses in normal operation, very high transition from superconducting to normal conductance and automatic triggering and recovering.

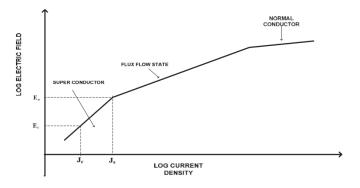

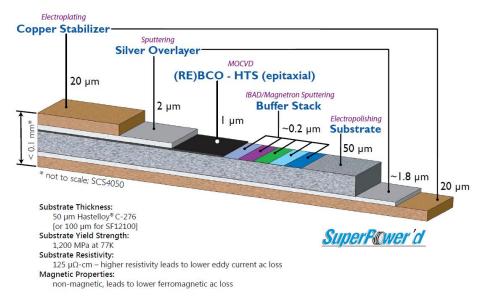

The most used superconducting materials in commercial FCL applications are, within the first generation HTS, the Bismuth Strontium Calcium Copper Oxide material (BSCCO), and, within the second generation of HTS, Yttrium Barium Coper Oxide material (YBCO) [26].

# 3.1 Superconducting fault current limiters

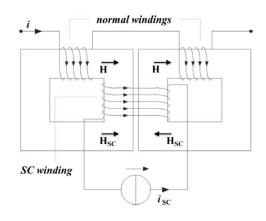

As stated in 2.5.2, current limiters are promising technology to cope with MTHV protection schemes. Current limiters are devices with negligible impedance in normal operation but under fault conditions they insert a series impedance (resistive or inductive), different technology types of current limiters are numbered in 1.2.1.

According to SFCL technology, there are different types [2]:

- Resistive type SFCL

- Inductive type SFCL

- DC reactor type SFCL

- Flux-locked type SFCL

- Vacuum interrupted based SFCL

- Matrix type SFCL

- Resonant type SFCL

- Bridge type SFCL

However, in general, they can be divided into resistive type and inductive type as they insert a resistive impedance or inductive impedance in series with the faulted circuit. The ideal current limiter requirements for HVDC system can be summarized as following [27]:

- Minimum impedance during normal operation. Resistance during normal operation would produce extra heating

- Fast fault current limitation, the FCL is required to change to high impedance in a short time to limit the peak or/and rise rate

- Quick automatic recovery

- Fail safe, in case of fail of the device it should limit the current

- Applicable to high voltages

- Cost effective

Superconducting FCL are appropriate considering these requirements. However, the two main obstacles for the development of this technology are the cryogenic cooling system and the superconductor material cost.

As stated in [27], the efficiency of the AL600 cryocooler at 30K is only 0.87% whilst at 80K is 5.21%, this power is small comparing with the total transmission power but economically is

not attractive. According to material cost, Table 7 shows typical HTS material price together with copper price as reference.

| Material | Nominal Operating Temperature [K] | Approximate material cost [\$/kAm] |

|----------|-----------------------------------|------------------------------------|

| Copper   | Tamb                              | 15-25                              |

| BSCCO    | 77                                | 180                                |

| YBCO     | 77                                | 400                                |

| MgB2     | 25                                | 13                                 |

Table 7 Price comparison of copper with superconducting materials

Note that even if MgB2 is much cheaper superconductor, the cryocooler efficiency drops for those temperatures.

Table 8 shows the latest projects up to 2016, the most active countries in the development of SFCL are South Korea, China, Germany, the UK and USA.

| MANUFACTURER   | DATA           | ТҮРЕ      | SUPERCONDUCTOR | FIELD<br>TEST | FUNCTION    |

|----------------|----------------|-----------|----------------|---------------|-------------|

| Innopower      | 220 kV, 300    | Saturated | BSCCO tape     | Yes           |             |

| (China)        | MVA            | core      |                | (2010)        |             |

| Kepco (Korea)  | 22.9 kV, 3 kA  | Hybrid    | YBCO tape      | No            | Transformer |

|                |                |           |                | (2010)        | protection  |

| Nexans         | 12 kV, 800 A   | Resistive | BSCCO bulk     | Yes           | Feeder      |

| (Germany)      |                |           |                | (2011)        | protection  |

| RSE (Italy)    | 9 kV, 3.4 MVA  | Resistive | BSCCO tape     | Yes           | Feeder      |

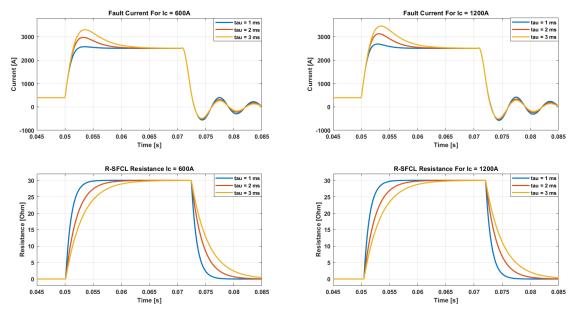

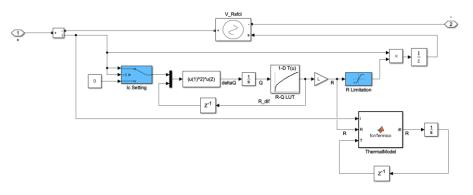

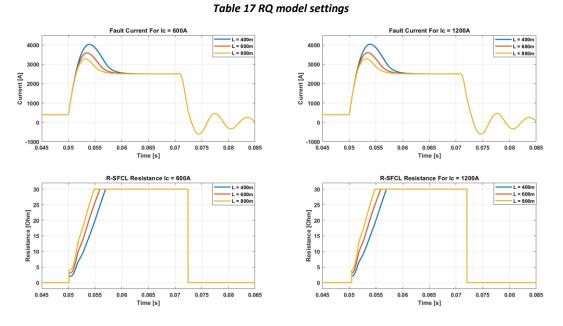

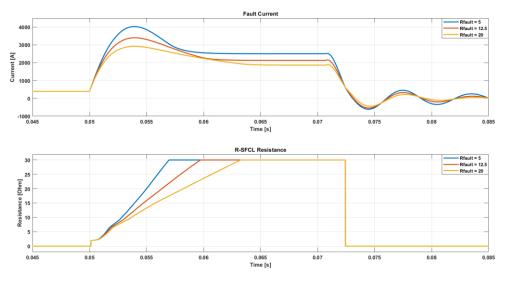

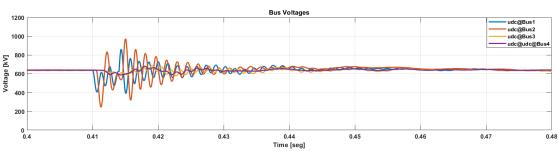

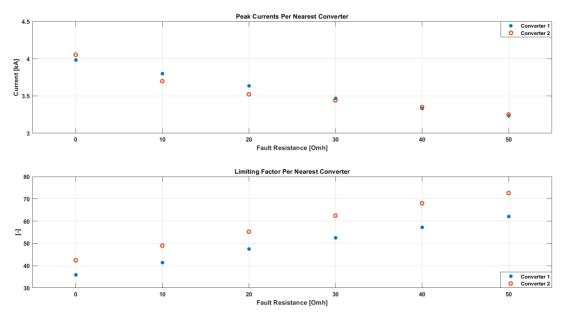

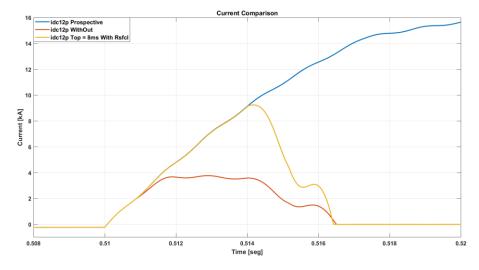

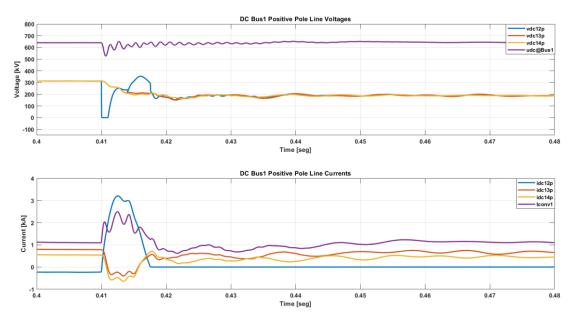

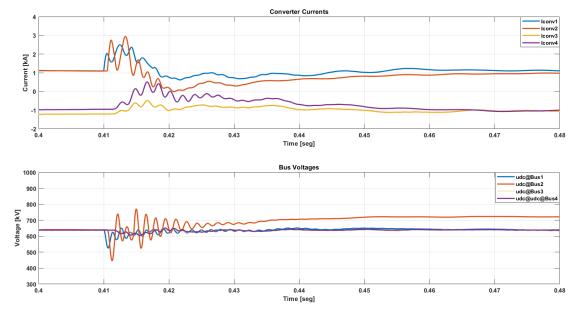

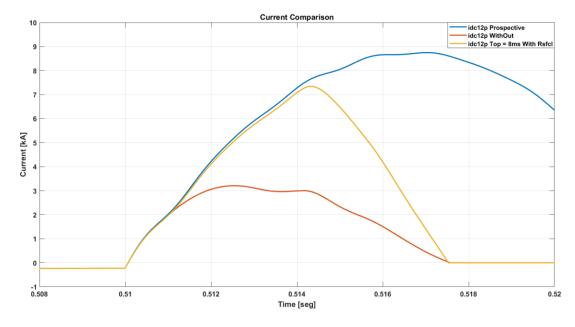

|                |                |           |                | (2012)        | protection  |